Università degli Studi di Milano CdL in Informatica per la comunicazione digitale AA 2025/2026

Architettura degli elaboratori - Lez 6 - A:

# Blocchi funzionali combinatori

Marco Tarini marco.tarini@unimi.it

1

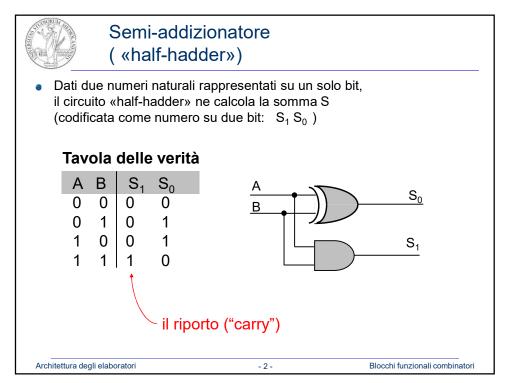

In pratica, lo half-adder implementa la "tabellina" della somma in base 2

+ 0 1

0 00 01

1 01 10

Il riporto ("carry")

Architettura degli elaboratori

-4

Aritmetica binaria

#### Full-adder

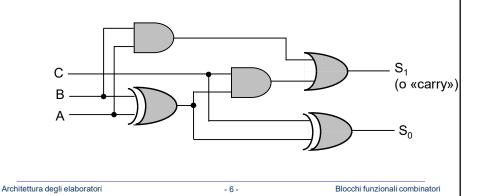

Dati tre numeri naturali rappresentati su un solo bit, questo circuito ne calcola la somma S (codificata con due BIT)

#### Tavola delle verità

| Α | В | С | S <sub>1</sub> | $S_0$ |

|---|---|---|----------------|-------|

| 0 | 0 | 0 | 0              | 0     |

| 0 | 0 | 1 | 0              | 1     |

| 0 | 1 | 0 | 0              | 1     |

| 0 | 1 | 1 | 1              | 0     |

| 1 | 0 | 0 | 0              | 1     |

| 1 | 0 | 1 | 1              | 0     |

| 1 | 1 | 0 | 1              | 0     |

| 1 | 1 | 1 | 1              | 1     |

|   |   |   |                |       |

$$S_1 = ABC + AB/C + /ABC + A/BC$$

=  $AB(C+/C) + C (/AB + A/B)$

=  $AB + C (A \oplus B)$

$$S_0 = A \oplus B \oplus C$$

Architettura degli elaboratori

- 5 -

Blocchi funzionali combinatori

5

## Full Adder: esempio di implementazione

$S_1$  = ABC + AB/C + /ABC + A/BC = AB(C+/C) + C (/AB + A/B) = AB + C (A $\oplus$ B)  $S_0$  = A  $\oplus$  B  $\oplus$  C

### Circuito addizionatore di interi a *n* bit: note per il lucido successivo 1/2

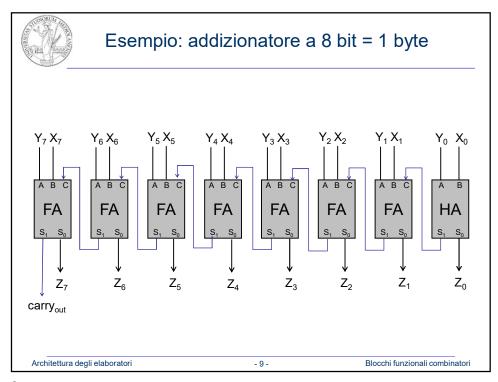

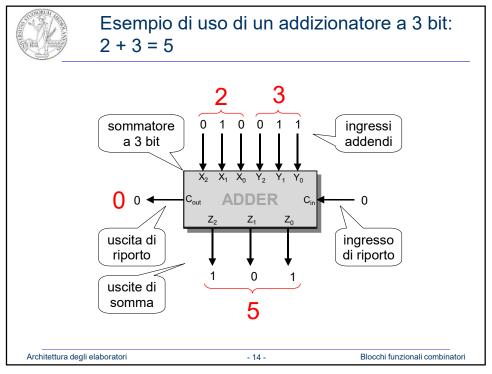

- Componendo insieme full-adder e half-adder posso costruire circuiti che sommano numeri in base 2 a n bit

- Questo ricalca il procedimento comune per sommare i numeri «in colonna» (con i riporti)

- Il primo Half-Adder calcola la somma della colonna «più a destra» (i due bit meno significativi)

- ▶ Ogni Full-Adder successivo calcola i due bit successivi, considerando il riporto

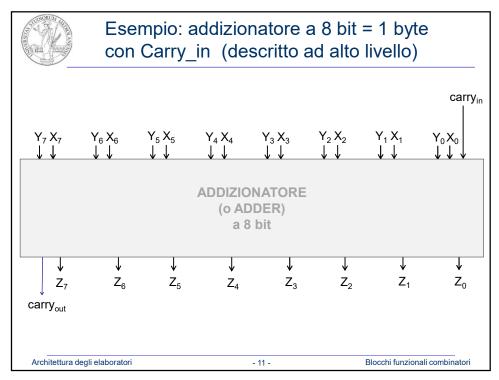

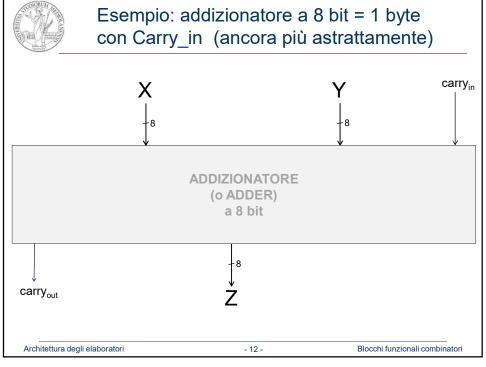

- Il circuito risultante

- ▶ prende in ingresso due numeri naturali X e Y da n 1 bit ciascuno

- presenta in uscita la loro somma a Z, da n bit ...

- ... e anche anche un «riporto in uscita» (Carry Out)

- ha quindi n+1 uscite in tutto

- Un addizionatore ottenuto in questo modo non è molto efficiente, ma è economico

- ▶ Il riporto deve attraversare tutto il circuito

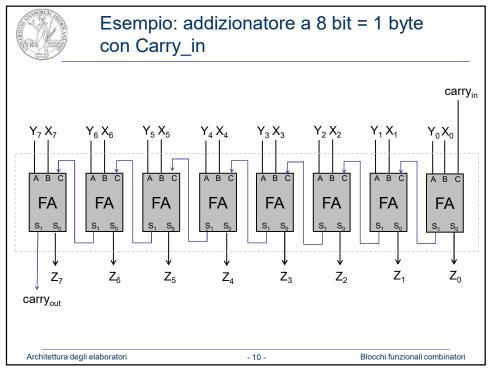

- Su uso un full-adder anche per la prima cifra, il circuito prende anche un riporto in ingresso (Carry-in) che viene normalmente messo a zero

- ▶ Il circuito somma anche il valore del Carry-in (0 o 1) all'output

Architettura degli elaboratori

- 8 -

Blocchi funzionali combinatori

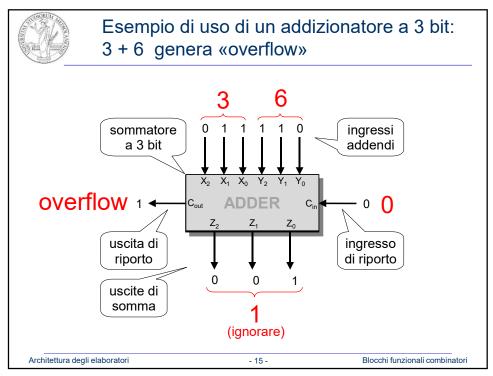

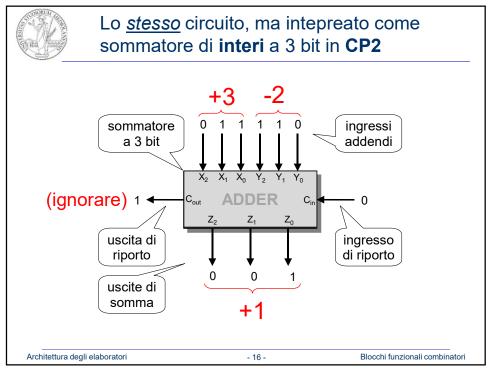

### Circuito addizionatore di interi a *n* bit: osservazione

- Come sappiamo, lo stesso circuito funziona anche per sommare due numeri con segno in complemento a due!

- Unica differenza:

- Quando sommo due numeri naturali: il bit «Carry Out» segnala l'overflow

- Quando sommo due numeri in CP2: il bit «Carry Out» va ignorato

Architettura degli elaboratori

- 13 -

Blocchi funzionali combinatori

13

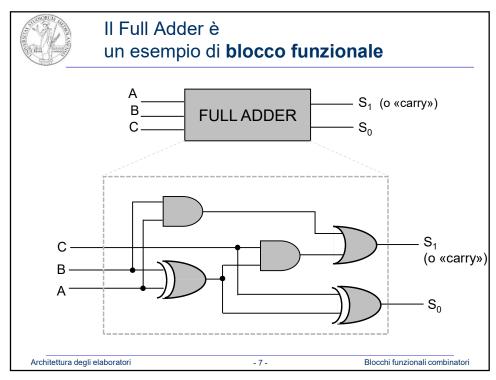

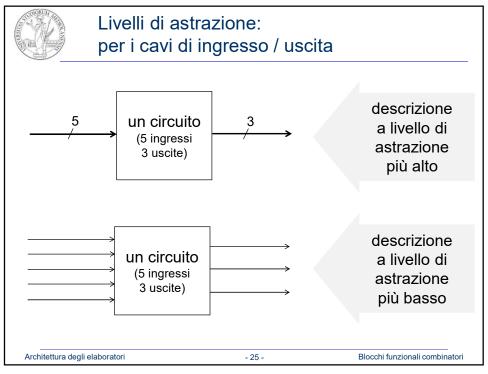

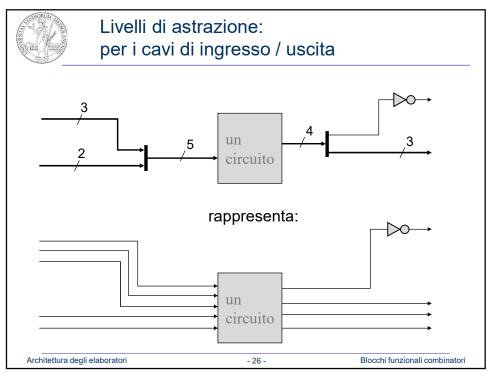

### Blocchi funzionali combinatori

- La realizzazione di moderni circuiti integrati richiede la sintesi di reti molto più grandi di quelle viste fin'ora

- Gestiamo la complessità attraverso livelli di astrazione

- Idea: combinare reti piccole in reti più grandi

- ▶ blocco funzionale = una sotto rete standard

- Ne sono esempi quelli visti:

- ▶ il Full Adder

- ▶ lo Half-Adder (componibile come visto per costruire un addizionatore a n bits)

- ➤ O a livello ancora più alto, un adder a n bits (come vedremo, compinibile per ottenere altri addizionatori a 2n bit)

- Esiste insieme di blocchi funzionali standard che risolvono problemi comuni, e risultano utili in contesti diversi. Vediamoli.

- (Esistono anche blocchi funzionali di tipo sequenziale, cioè non combinatorio, che vedremo in seguito)

Architettura degli elaboratori

- 24

Blocchi funzionali combinatori

24

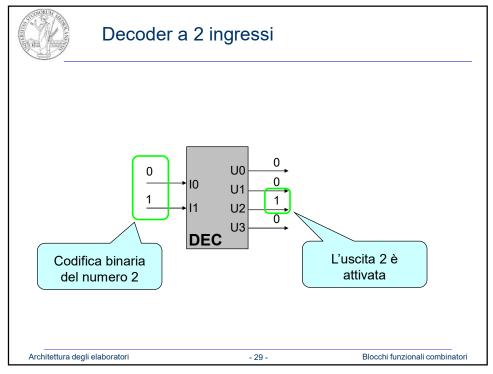

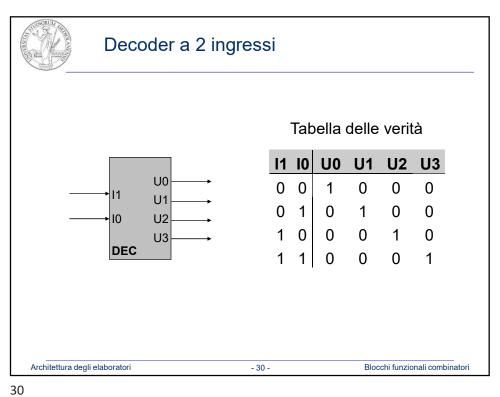

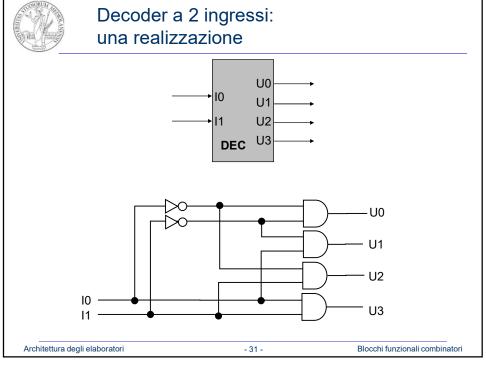

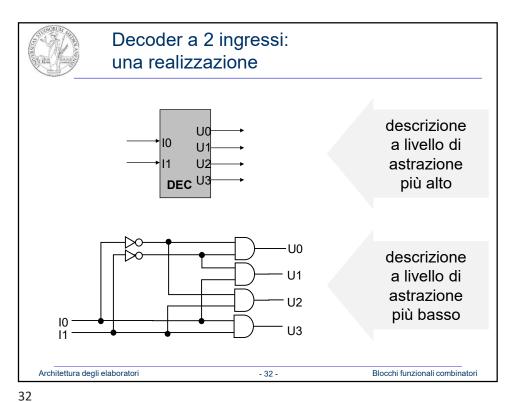

### Decoder (decodificatore)

- Il blocco funzionale «decodificatore» ha:

- n ≥ 1 ingressi

- 2<sup>n</sup> uscite

- Le uscite sono numerate a partire da 0

- $k = 0, 1, 2, ..., 2^{n-1}$

- Se sugli ingressi è presente il numero binario k

- la k-esima uscita assume il valore 1

е

le restanti uscite assumono il valore 0

Architettura degli elaboratori

- 28 -

Blocchi funzionali combinatori

28

Multiplexer (selezionatore) a due vie Rappresentazioni grafica usate: E' blocco funzionale che ha in ingresso ▶ un ingresso A0 di n bit ▶ un ingresso A1 di n bit ▶ 1 bit di selezione S (il selezionatore) E in uscita: ▶ un canale B di *n* bit Funzionamento: ▶ Il canale B vale A0 oppure A1, a seconda del valore di S S «sceglie» fra A0 e A1 ▶ Se S = 0, esce A0 ▶ Se S = 1, esce A1 Architettura degli elaboratori - 35 -Blocchi funzionali combinatori

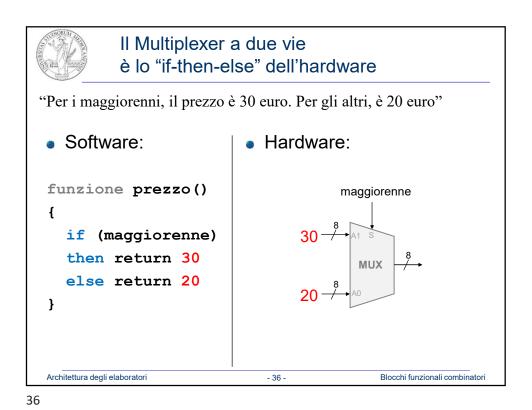

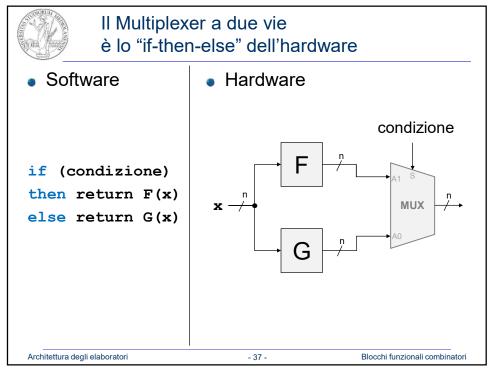

### Il Multiplexer a due vie è lo "if-then-else" dell'hardware

- Osservazioni:

- In software, solo uno fra il ramo then e il ramo else viene computato

- ▶ In hardware, entrambi i casi sono computati, e solo uno dei due risultati è passato in output. L'altro, viene scartato dal Multiplexer.

- Questo può sembrare uno spreco, ma va considerato che i due rami sono, almeno, computati in parallelo

- Vediamo dalla prossima volta come implementare un multiplexer

Architettura degli elaboratori

- 38 -

Blocchi funzionali combinatori

38

### Esercizi e domande di repilogo

- Capire bene e nel dettaglio gli esempi che non abbiamo visto in aula:

- ▶ l'addizionatore (a tre bit) usato per la somma in Complemento a 2

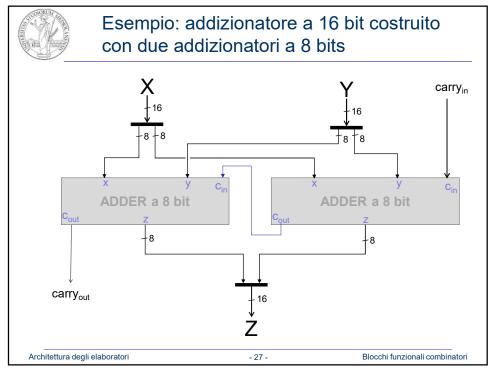

- ▶ l'esempio dell'addizionatore a 16 bit progettato usando, come blocchi funzionali, due addizionatori a 8 bit

- Domanda: nell'addizionatore a 8 bit, il passaggio dei riporti costituiscono delle "retroazioni"?

- ▶ In quello dell'addizionatore a 16 bit, il passaggio del riporto costitusce una "retroazione"?

- Scrivi la tabella di verità di un multiplexer a due vie a 1 bit (cioè, per due segnali di un solo bit bit).

Disegna il circuito corrispodente.

- ▶ [solo per chi ha pazienza] ripetere, per due segnali di 2 bit.

Architettura degli elaboratori

- 39 -

Blocchi funzionali combinatori