Università degli Studi di Milano «La Statale»

Dipartimento di Informatica

Lezione 12:

## CPU e linguaggio MIPS

### Parte C: istruzioni di tipo «I»

Marco Tarini

55

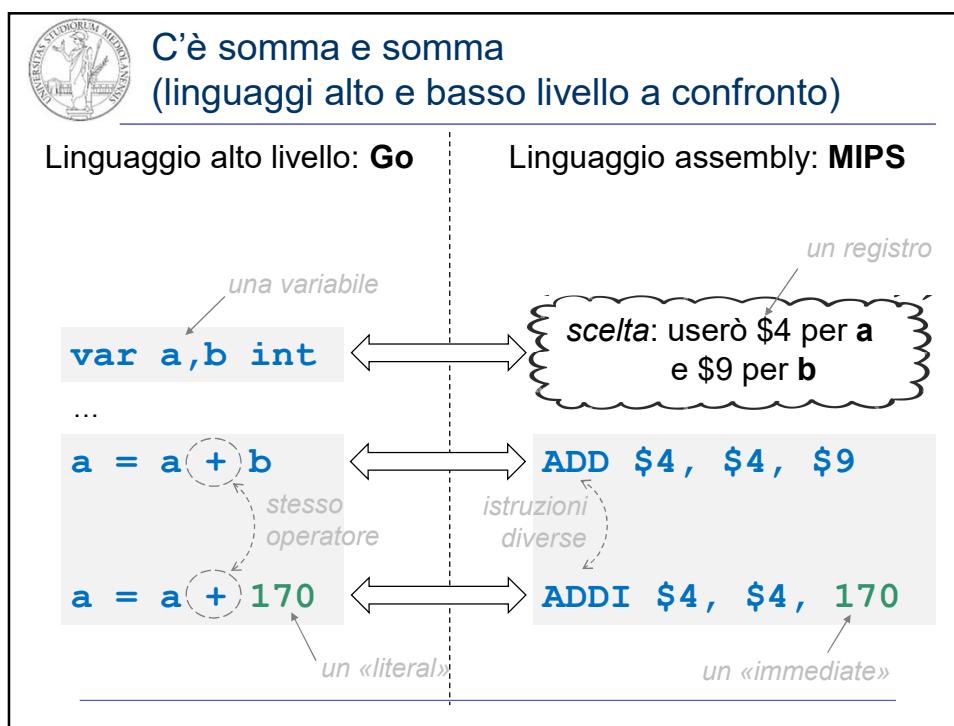

Prossima istruzione di cui vogliamo dotarci

Istruzione assembly già vista: **ADD \$30, \$6, \$11**

A parole: « *Somma il Registro 6 al Registro 11

e memorizza il risultato nel Registro 30* »

Istruzione assembly nuova: **ADDI \$30, \$3, 240**

A parole: « *Somma il Registro 3 con il valore 240

e memorizza il risultato nel Registro 30* »

valore

“immediato”

- 58 -

58

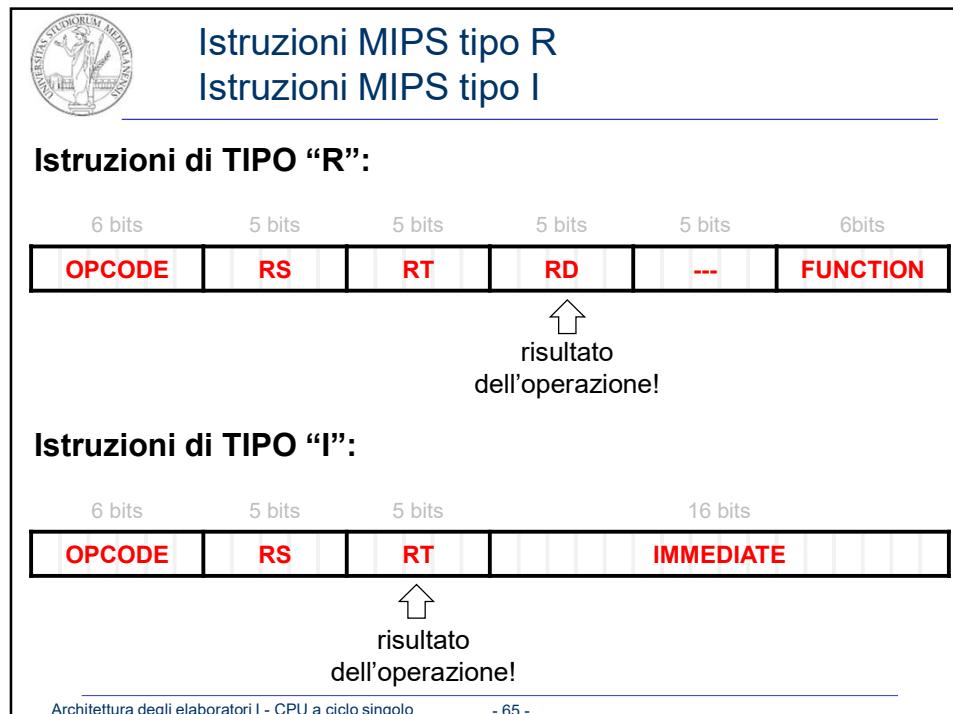

**In linguaggio macchina MIPS:**

**ADD \$30, \$6, \$11**      istruzione di tipo "R" (registro)

|                                                                  |

|------------------------------------------------------------------|

| 0 0 0 0 0 0 0 0 1 1 0 0 1 0 1 1 1 1 1 1 0 0 0 0 0 0 1 0 0 0 0 0  |

| Operazione fra registri      6      11      30      ---      SUM |

| OPCODE      RS      RT      RD      ---      FUNCTION            |

**ADDI \$30, \$3, 240**      istruzione di tipo "I" (immediato)

|                                                                   |

|-------------------------------------------------------------------|

| 0 0 1 0 0 1 0 0 0 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 0 1 1 1 1 0 0 0 0 |

| Add register to immediate      3      30      240                 |

| OPCODE      RS      RT      IMMEDIATE (16 bits)                   |

59

60

Un'altra istruzione di tipo “I”

The diagram shows the 32-bit MIPS I-type instruction format. The first 6 bits are the OPCODE (001110). The next 5 bits are the RS field (00011). The next 5 bits are the RT field (01010). The remaining 16 bits are the IMMEDIATE field (00000000001111100000).

|                                   |           |           |                            |

|-----------------------------------|-----------|-----------|----------------------------|

| XOR between register to immediate | 3         | 11        | 240                        |

| <b>OPCODE</b>                     | <b>RS</b> | <b>RT</b> | <b>IMMEDIATE (16 bits)</b> |

Tradotta in assembly MIPS: **XORI \$11, \$3, 240**

A parole: « *Fai lo XOR bit-a-bit fra il Registro 3 e 0..011110000 e memorizza il risultato nel Registro 11* »

61

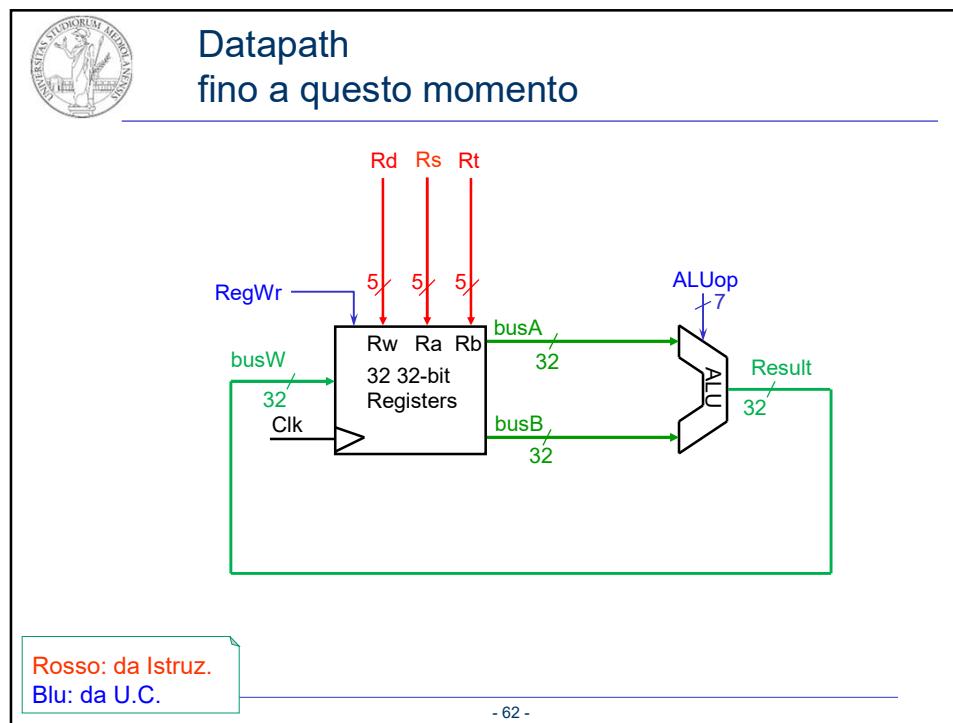

- 62 -

62

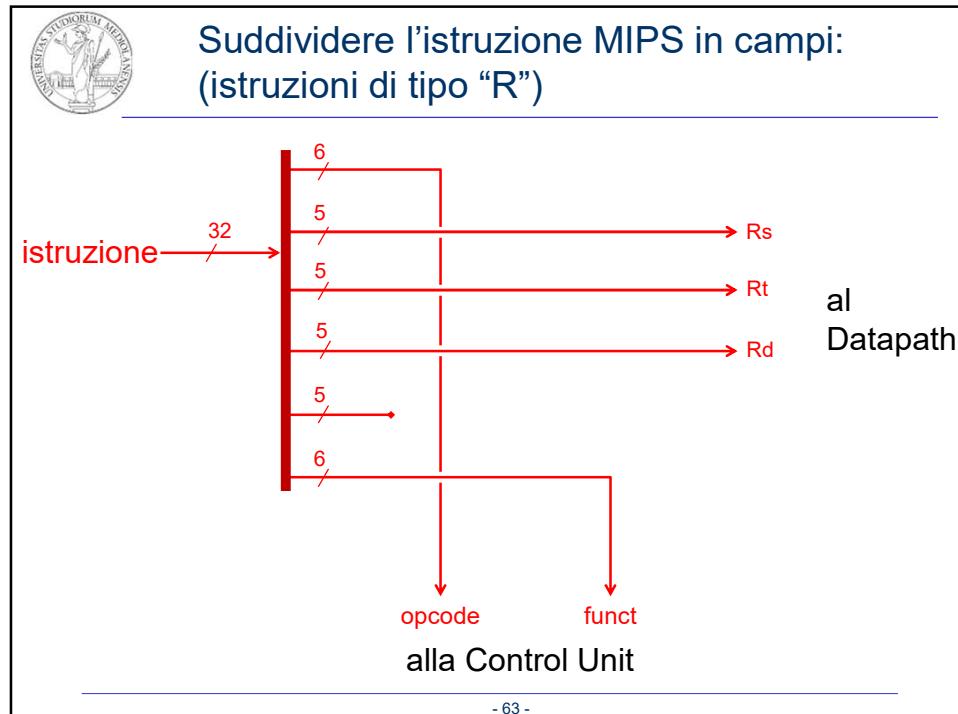

63

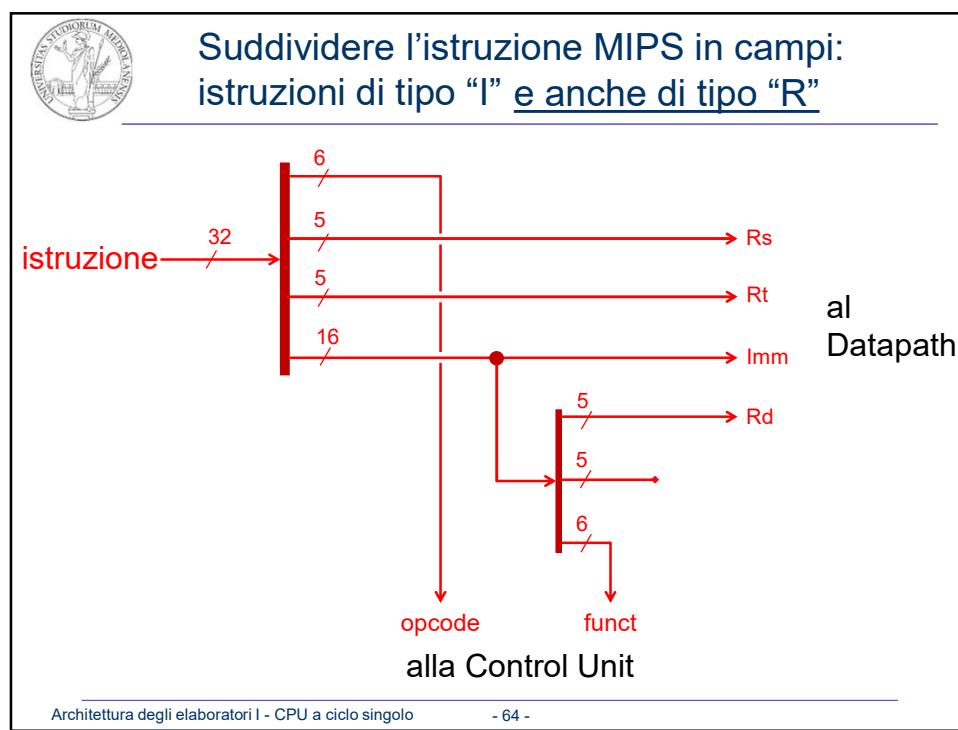

64

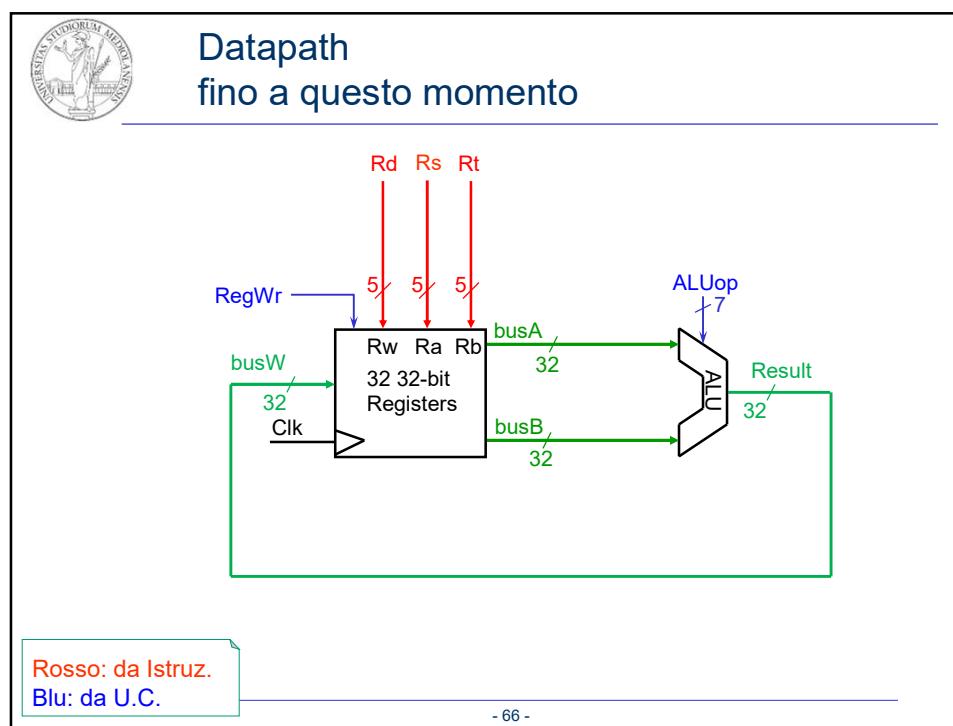

65

66

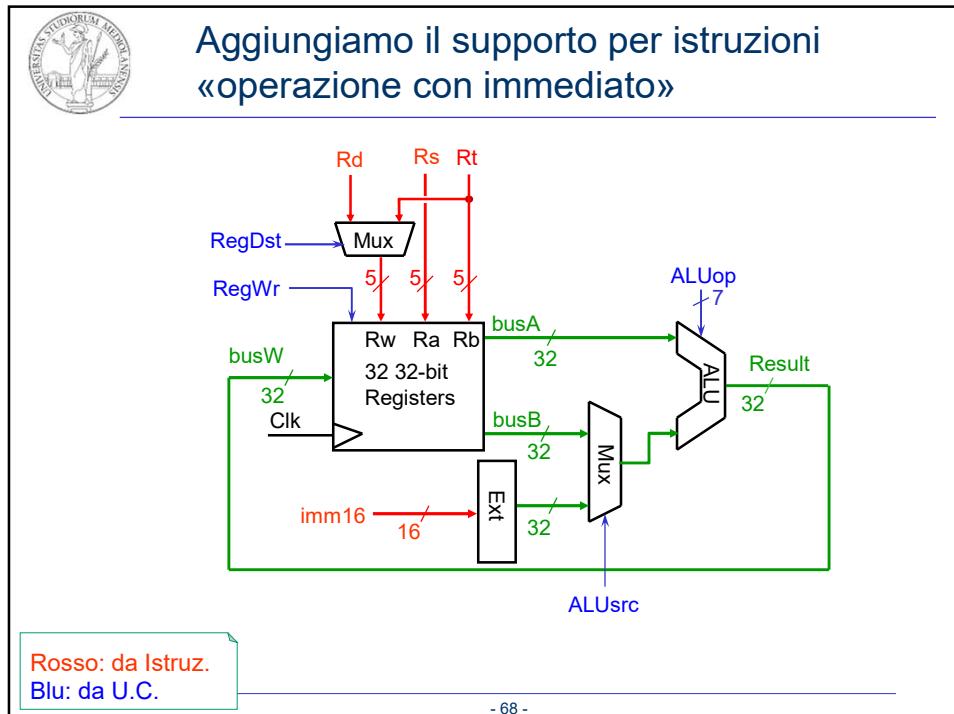

68

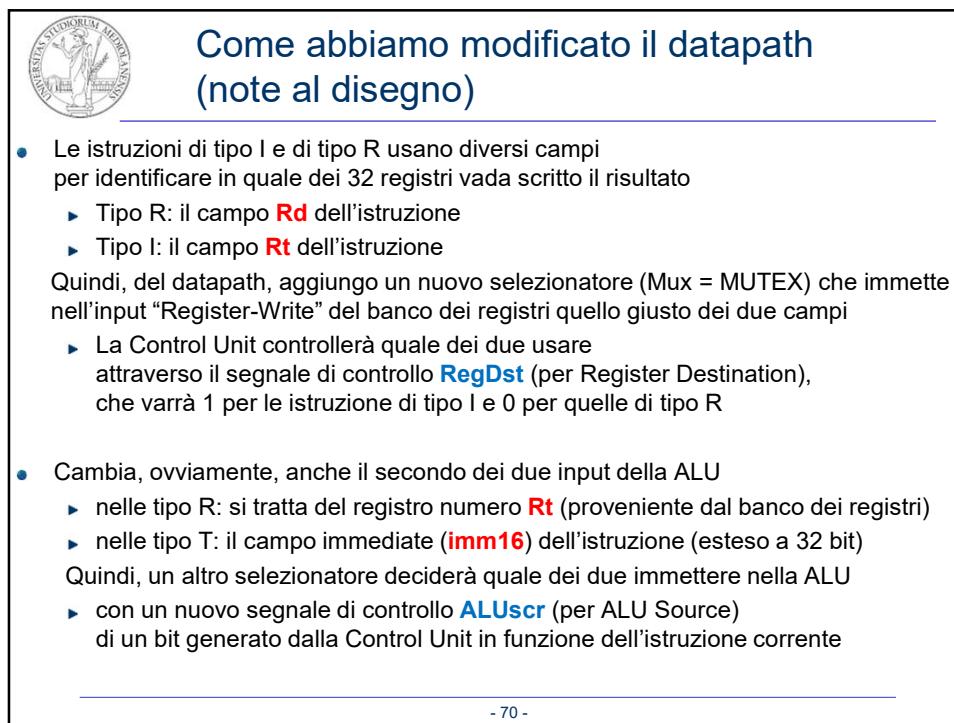

70

71

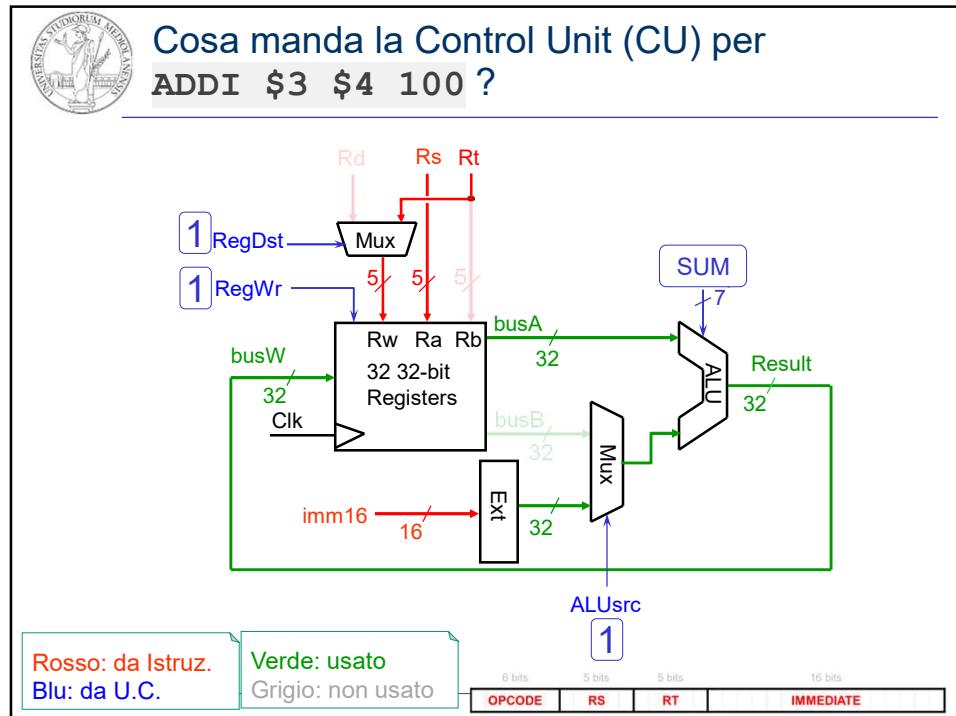

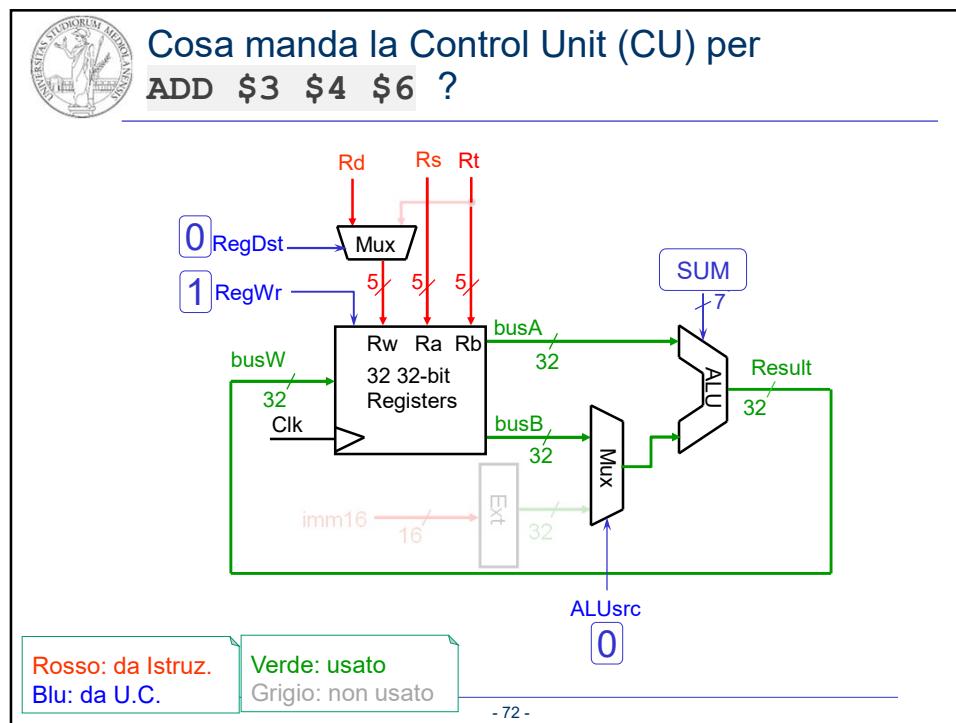

72

| Alcune istruzioni aritmetiche-logiche<br>di tipo I ("I = con immediate") |                                |                             |                                        |

|--------------------------------------------------------------------------|--------------------------------|-----------------------------|----------------------------------------|

| Istruzione                                                               | Sintassi assembly<br>(esempio) | Semantica<br>(dell'esempio) | Note                                   |

| <b>add immediate</b>                                                     | <b>addi \$1 \$2 150</b>        | $\$1 = \$2 + 150$           | Check di overflow                      |

| <b>add immediate unsigned</b>                                            | <b>addiu \$1 \$2 150</b>       | $\$1 = \$2 + 150$           | Niente check                           |

| <b>or immediate</b>                                                      | <b>ori \$1 \$2 35</b>          | $\$1 = \$2 \vee 35$         | Bit a bit<br>(in inglese:<br>bit-wise) |

| <b>and immediate</b>                                                     | <b>andi \$1 \$2 35</b>         | $\$1 = \$2 \wedge 35$       |                                        |

| <b>xor immediate</b>                                                     | <b>xori \$1 \$2 35</b>         | $\$1 = \$2 \oplus 35$       |                                        |

| <b>shift logical left</b>                                                | <b>sll \$1 \$2 9</b>           | $\$1 = \$2 \ll 9$           |                                        |

| <b>shift logical right</b>                                               | <b>slr \$1 \$2 9</b>           | $\$1 = \$2 \gg 9$           | da sx spunta 0                         |

| <b>shift arithmetical right</b>                                          | <b>sar \$1 \$2 9</b>           | $\$1 = \$2 \gg 9$           | da sx spunta il MSB                    |

73

| E la differenza con immediate?                                                      |                                                 |  |  |

|-------------------------------------------------------------------------------------|-------------------------------------------------|--|--|

|  |                                                 |  |  |

| ● Nuovamente, filosofia RISC in azione.                                             |                                                 |  |  |

| ● Invece di                                                                         |                                                 |  |  |

| <b>SUBI \$3 \$4 150</b>                                                             | <b>&lt;= Subtract Immediate?</b>                |  |  |

|                                                                                     | non esiste (no, neanche come pseudo istruzione) |  |  |

| basta usare                                                                         |                                                 |  |  |

| <b>ADDI \$3 \$4 -150</b>                                                            |                                                 |  |  |

- 74 -

74

## Operazioni di shift con 2° operando costante: nome dell'istruzione in assembly

- Nome dell'istruzione assembly (e del codice mnemonico):

- ▶ quando il 2° operando è un registro (operazione di tipo R)

le operazioni di shift si chiamano «shift ... variable» (v nel codice mnemonico)

- ▶ quando il 2° operando è costante (un immediate),

non c'è «variable» nel nome

- Questo è un po' inconsistente con quello che succede con le altre operazioni

- Paragona:

| <i>con 2° parametro registro</i>    | <i>con 2° parametro immediate</i> |

|-------------------------------------|-----------------------------------|

| add                                 | add immediate                     |

| xor                                 | xor immediate                     |

| shift logical right <b>variable</b> | shift logical right               |

| shift logical left <b>variable</b>  | shift logical left                |

75

## Operazioni di shift con 2° operando costante: in linguaggio macchina (mini-dettaglio)

- **Confessione:** (per la precisione)

- ▶ In questo corso, semplifichiamo un po' la cose rispetto al reale linguaggio macchina MIPS-32 (come definito dallo standard)

- ▶ Nel linguaggio reale, le istruzioni di *shift* non *variable*, come **shift logical left**, sono anch'esse di «tipo R», come quelle *variable*

- ▶ Il 2° operando non è il campo «immediate» di una istruzione di «tipo I»

Invece è nascosto qui, il quel campo di 5 bit delle «tipo R» che abbiamo ignorato:

*SLL \$5, \$12, 6*

La reale traduzione in linguaggio macchina:

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|                     |    |          |    |           |                  |

|---------------------|----|----------|----|-----------|------------------|

| Operaz fra Registri | 12 | (unused) | 5  | 6         | Shift a sinistra |

| OPCODE              | RS | RT       | RD | SHIFT VAL | FUNCTION         |

- 76 -

76

## Come scrivere gli **immediate** in assembly MIPS (cioè: sintassi dei *literal* di quel linguaggio)

- Come abbiamo visto, un valore immediate consiste in 16 bit

- In assembly, posso descrivere il valori immediate in vari modi:

In base 10:

`ADDI $3 $4 150`

Incluso, con segno (verrà tradotto in CP2)!

`ADDI $3 $4 -150`

Oppure in base 16:

`ADDI $3 $4 0xABBA`

Oppure usando il carattere del numero in codice ASCII (nota gli apicetti)

`ADDI $3 $4 '!'`

In ciascun caso, l'**assembler** traduce il «**literal**» in 16 bit,

quando volge l'istruzione in **linguaggio macchina** (grazie, assembler!)

- 77 -

77

## Inizializzazione esplicita dei registri

- Come caricare dei valori nei registri?

- Esempio:

- ▶ caricare in \$6 il valore 27

- L'Instruction Set MIPS è così RISC che

*non ha un'istruzione per inizializzare i registri!*

- Questo perché possiamo utilizzare (fra altre possibilità)

l'istruzione «somma fra registro e valore immediato»

`addi $6 $0 27`

Registro speciale,

il cui valore è sempre 0

78

Inizializzazione esplicita dei registri:

la pseudo istruzione Load immediate

- Questa soluzione però è poco leggibile

- il linguaggio assembly MIPS ci mette quindi a disposizione una **pseudo-istruzione** più chiara per ottenere lo stesso effetto:

«Load immediate»

↓

li \$6 27

↓ TRADUZIONE AUTOMATICA

effettuata dell'assembler

addiu \$6 \$0 27

79

Inizializzazione esplicita dei registri:

la pseudo istruzione Load immediate

- Problema: il campo immediate è di soli 16 bit.

- ▶ Viene esteso con 0 per riempire il registro di 32 bit

- A volte, vogliamo inizializzare *tutti i 32 bit* di un registro. Come fare?

- Ad esempio, come inizializziamo il registro \$9 al valore 0xABCD1234 ?

li \$9 0xABCD1234

↓ TRADUZIONE AUTOMATICA

effettuata dall'assembler

addiu \$9 \$0 0xABCD      \$9 ← 0x 0 0 0 0 A B C D

sll      \$9 \$9 16      \$9 ← 0x A B C D 0 0 0 0

ori      \$9 \$9 0x1234      \$9 ← 0x A B C D 1 2 3 4

80

Inizializzazione esplicita dei registri:

la pseudo istruzione Load immediate

- Ottimizzazione: per risparmiare un'istruzione nel programma, il MIPS mette a disposizione un'apposta istruzione detta «load upper immediate» (lui)

- la sua implementazione HW: è solo un'altra funz prevista dalla ALU

**li \$9 0xABCD1234**

TRAUDUZIONE AUTOMATICA

effettuata dall'assembler

**lui \$9 0xABCD**       $\$9 \leftarrow 0x \boxed{A \ B \ C \ D \ 0 \ 0 \ 0 \ 0}$

**ori \$9 \$9 0x1234**       $\$9 \leftarrow 0x \boxed{A \ B \ C \ D \ 1 \ 2 \ 3 \ 4}$

81

Estensione con 0 VS estensione in segno

(ripasso, con un esempio)

|                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>In binario senza segno</b>                                                                                                                                                            | <b>In complemento a 2</b>                                                                                                                                                                                                                                                                                             |

| <ul style="list-style-type: none"><li>• Su 4 bit:<br/><b>1101</b><br/>denota tredici;</li><li>• allora su 8 bit<br/><b>00001101</b><br/>denota ancora tredici<br/>(banalmente)</li></ul> | <ul style="list-style-type: none"><li>• Su 4 bit,<br/>per i positivi: <b>0101</b><br/>denota più cinque;</li><li>• allora su 8 bit: <b>00000101</b><br/>denota ancora più cinque</li><li>• per i negativi: <b>1101</b><br/>denota meno tre;<br/>allora su 8 bit: <b>11111101</b><br/>denota ancora meno tre</li></ul> |

| <ul style="list-style-type: none"><li>• <b>Per estendere<br/>basta aggiungere tanti 0 a sx</b></li><li>• detta «estensione con 0»</li></ul>                                              | <ul style="list-style-type: none"><li>• <b>Per estendere,<br/>basta ripetere il MSB a sx</b></li><li>• detta «estensione in segno»</li></ul>                                                                                                                                                                          |

Architettura degli elaboratori I - CPU a ciclo singolo      - 82 -

82

**Nei comandi matematici,

l'immediate è in CP2**

|                                                                  |           |           |                            |

|------------------------------------------------------------------|-----------|-----------|----------------------------|

| <b>0 0 1 0 0 1 0 0 0 1 1 0 1 0 1 1 1 1 1 1 1 1 0 0 0 1 0 0 0</b> |           |           |                            |

| Add<br>register<br>to immediate                                  | 3         | 11        | -240<br><i>è in CP2!</i>   |

| <b>OPCODE</b>                                                    | <b>RS</b> | <b>RT</b> | <b>IMMEDIATE (16 bits)</b> |

Tradotta in assembly MIPS: **ADDI \$11, \$3, -240**

A parole: « *Somma il valore -240 al Registro 3

e memorizza il risultato nel Registro 11* »

Architettura degli elaboratori I - CPU a ciclo singolo      - 83 -

83

**Nei comandi logici,

l'immediate è senza segno**

|                                                                    |           |           |                            |

|--------------------------------------------------------------------|-----------|-----------|----------------------------|

| <b>0 0 1 1 1 0 0 0 0 1 1 0 1 0 1 1 0 0 0 0 0 0 0 1 1 1 1 0 0 0</b> |           |           |                            |

| XOR between<br>register<br>to immediate                            | 3         | 11        | 240<br><i>non è in CP2</i> |

| <b>OPCODE</b>                                                      | <b>RS</b> | <b>RT</b> | <b>IMMEDIATE (16 bits)</b> |

Tradotta in assembly MIPS: **XORI \$11, \$3, 240**

A parole: « *Fai lo XOR bit a bit fra il Registro 3 e 0..011110000

e memorizza il risultato nel Registro 11* »

Architettura degli elaboratori I - CPU a ciclo singolo      - 84 -

84

## Operazioni con immediate in MIPS: matematiche VS logiche

- In MIPS, nei comandi con immediate **matematici** (come ADD) il parametro *immediate* va interpretato in CP2

- ▶ E di conseguenza va esteso (a 32 bit) **in segno**

- ▶ La quantità Immediate può essere quindi sia positiva che negativa

- ▶ Scelta strategica dell'IS!

Riduce il numero di operazioni nell'IS (filosofia RISC in azione).

- ▶ Non ci sarà infatti bisogno di un'operazione "SUBI" (per sottrarre con Immediate): basterà ADD-izionare con valori imm. negativi

- ▶ Nota: c'è comunque bisogno di un'operazione SUB fra registri, distinta da ADD, per eseguire sottrazioni *fra registri*

- Invece nelle comandi **logici** (come XOR o AND) il parametro immediate non è in CP2 e quindi va esteso **con zero**

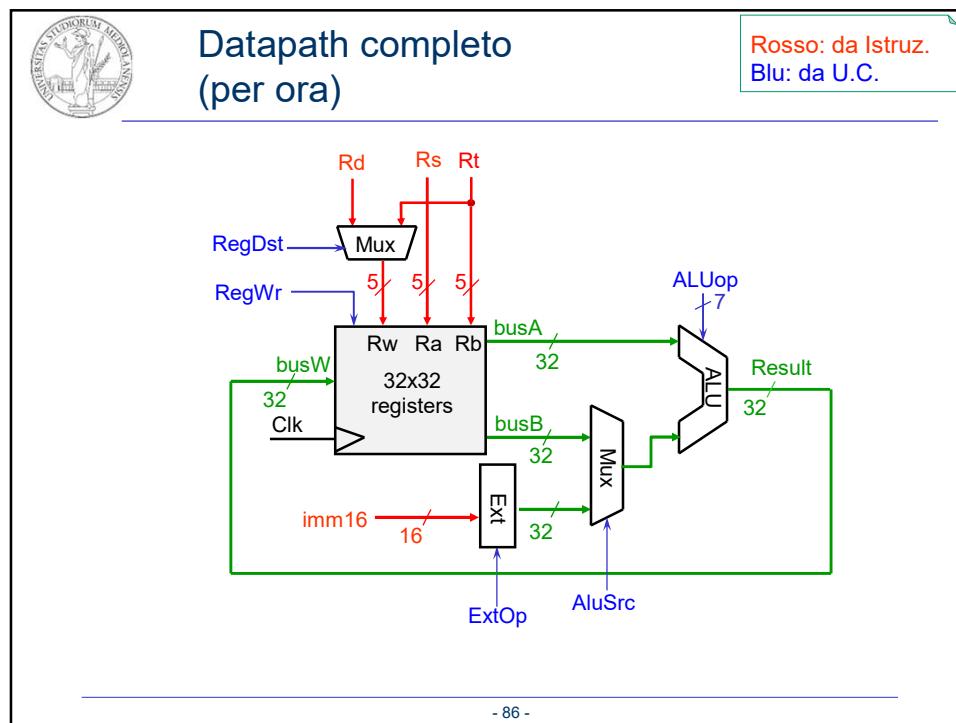

- Come gestire la diversa modalità di estensione? Risposta:

- ▶ La Control Unit "sceglie" come va esteso, a seconda di OP-Code, mandando un apposito comando al datapath (chiamiamolo "**extOp**")

- ▶ Nel datapath questo comando determina il comportamento di un **Estesore a scelta** (vedi lezione sui blocchi logici)

Architettura degli elaboratori I - CPU a ciclo singolo      - 85 -

85

86