Università degli Studi di Milano «La Statale»

Dipartimento di Informatica

Lezione 12:

**CPU e

linguaggio MIPS**

Parte D: load and store (RAM)

---

Marco Tarini

87

### Ripasso: scambi di memoria fra registri e Main Memory

- I dati che i nostri programmi devono elaborare sono molti numerosi di più di quelli che registri possono mantenere

- Il grosso dei dati è memorizzato in Main Memory (RAM)

- ▶ puro storage di dati, senza capacità di elaborazione diretta

- Scambio di dati avviene attraverso operazioni di **LOAD** e **STORE**

- ▶ Copiano *un word alla volta*

- ▶ Il linguaggio macchina MIPS supporta questi comandi (stiamo per vedere come)

- ▶ Il linguaggio assembly MIPS prevede le istruzioni corrispondenti (vediamo con quale sintassi)

RAM

88

## Istruzione MIPS per load da memoria

Tradotta in assembly MIPS: **LW \$5, (\$14)**

A parole: « *Accedi la memoria RAM in lettura all'indirizzo contenuto nel Registro 14, e memorizza la parola letta nel Registro 5* »

- 89 -

89

## Istruzione MIPS per load da memoria: note

- In **linguaggio macchina**: l'indirizzo di memoria al quale accedere (di 32 bit) non può essere contenuto nell'istruzione (lunga 32 bit in tutto)

- ▶ Invece, la Load Word specifica un registro che *contiene* questo indirizzo

- In **assembly**: il 1° argomento è il registro che sovrascriviamo (come al solito)

- In **assembly**: la sintassi richiede di incapsulare 2° argomento, cioè il registro che contiene l'indirizzo di RAM, fra parentesi tonde

- ▶ Questo è il modo di questo linguaggio assembly per aiutarci a ricordare che ha luogo una «**indirezione**»

- ▶ Cioè che, nell'esempio, scriviamo in \$5 non *il word contenuto del registro \$14* ma *il word in RAM che ha come indirizzo il word contenuto nel registro \$14*

- Cioè: *direttamente* il valore di \$14 ma *indirettamente* il valore di RAM a quell'indirizzo.

- ▶ Valore che possiamo denotare con **RAM[ \$14 ]** , usando la notazione che hai visto nel corso di programmazione per gli “array” (o “vettori”)

Nota il termine

- 90 -

90

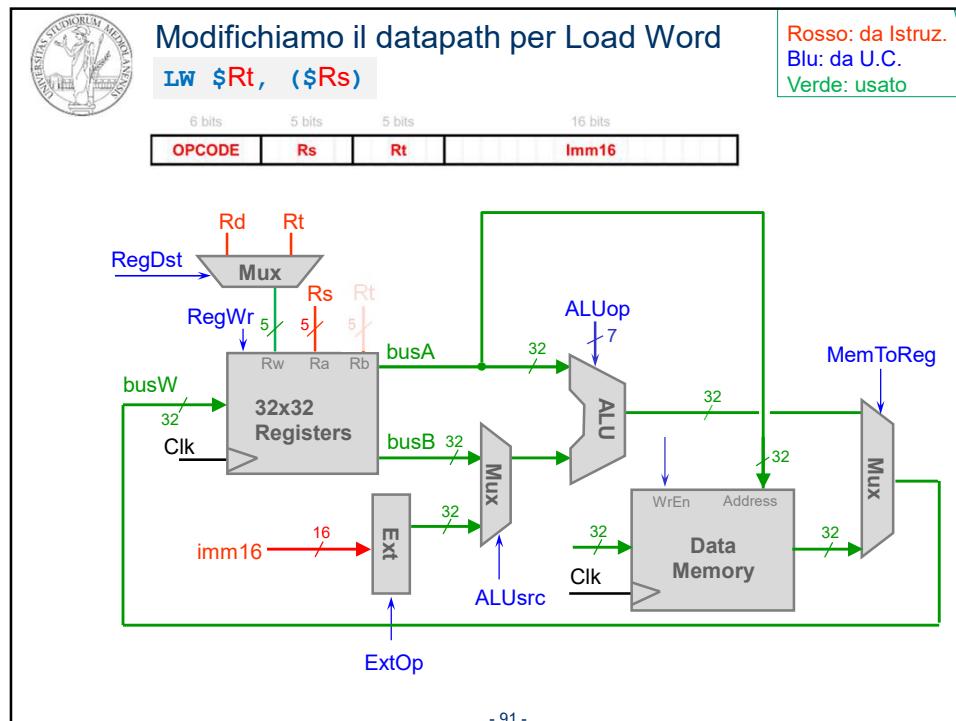

91

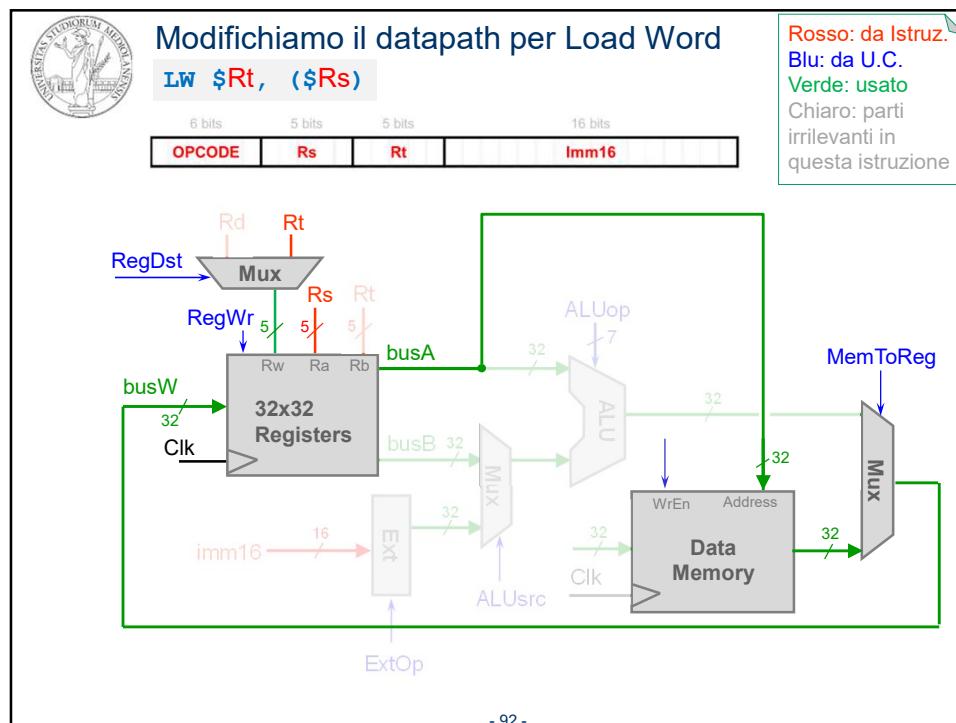

92

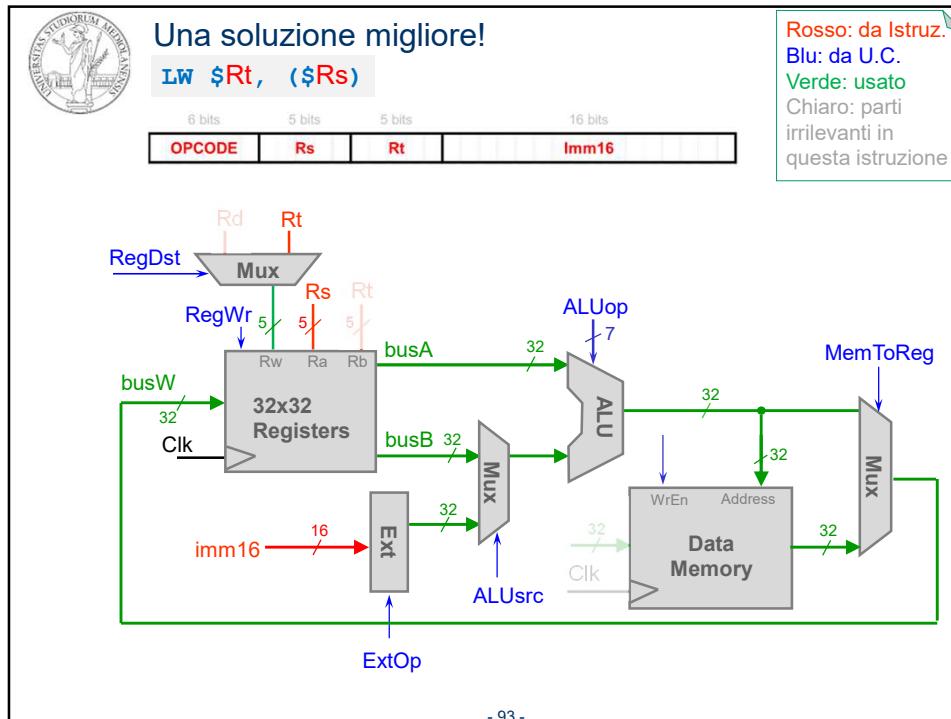

93

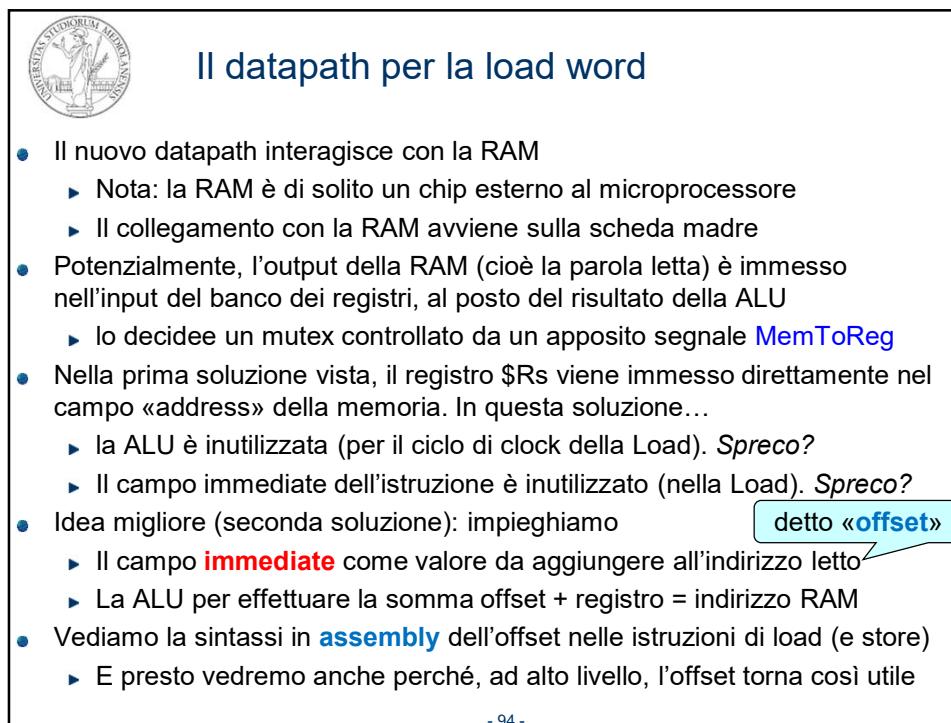

94

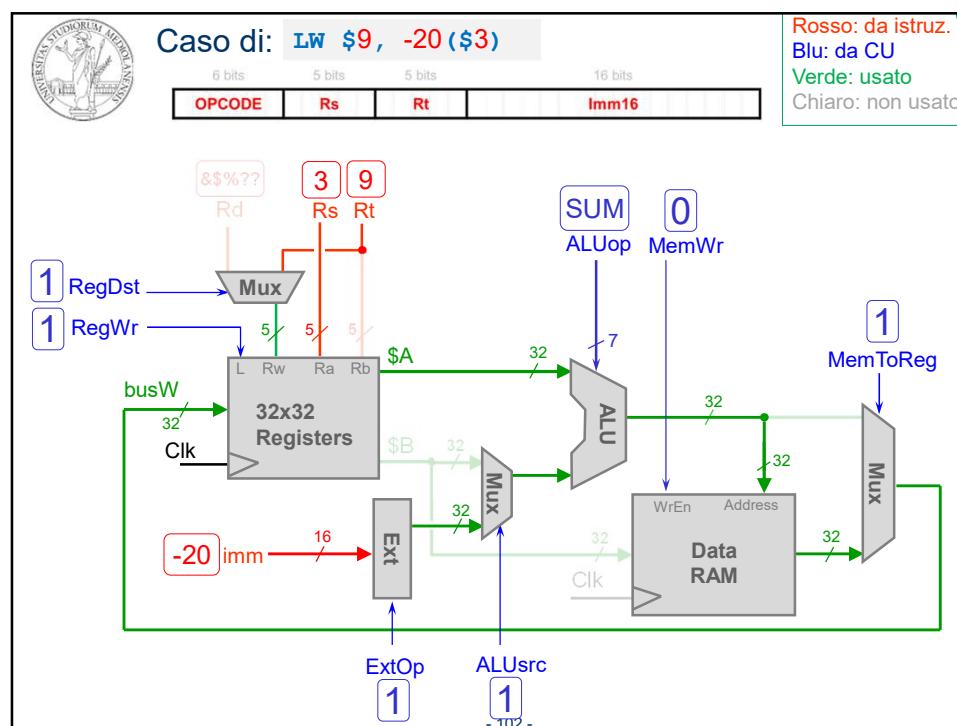

### Prossimo esempio di istruzione MIPS

|           |    |   |   |   |   |   |    |   |   |   |   |   |                     |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|-----------|----|---|---|---|---|---|----|---|---|---|---|---|---------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1         | 0  | 0 | 0 | 1 | 1 | 0 | 1  | 1 | 1 | 0 | 0 | 0 | 1                   | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 |

| Load Word | 14 |   |   |   |   |   | 5  |   |   |   |   |   | 240                 |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| OPCODE    | RS |   |   |   |   |   | RT |   |   |   |   |   | IMMEDIATE (16 bits) |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

Tradotta in assembly MIPS: **IW \$5, 240(\$14)**

A parole: « *Somma 240 al Registro 14,

accedi la memoria RAM all'indirizzo che hai ottenuto;

memorizza la parola letta nel Registro 5* »

- 95 -

95

### Prossimo esempio di istruzione MIPS

|           |    |   |   |   |   |   |    |   |   |   |   |   |                     |   |   |   |   |   |           |   |   |   |   |   |   |   |

|-----------|----|---|---|---|---|---|----|---|---|---|---|---|---------------------|---|---|---|---|---|-----------|---|---|---|---|---|---|---|

| 1         | 0  | 0 | 0 | 1 | 1 | 0 | 1  | 1 | 1 | 0 | 0 | 0 | 1                   | 0 | 1 | 1 | 1 | 1 | 1         | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| Load Word | 14 |   |   |   |   |   | 5  |   |   |   |   |   | -1                  |   |   |   |   |   | è in CP2! |   |   |   |   |   |   |   |

| OPCODE    | RS |   |   |   |   |   | RT |   |   |   |   |   | IMMEDIATE (16 bits) |   |   |   |   |   |           |   |   |   |   |   |   |   |

Tradotta in assembly MIPS: **IW \$5, -1(\$14)**

A parole: « *Togli 1 al Registro 14

accedi la memoria RAM all'indirizzo che hai ottenuto;

memorizza la parola letta nel Registro 5* »

- 96 -

96

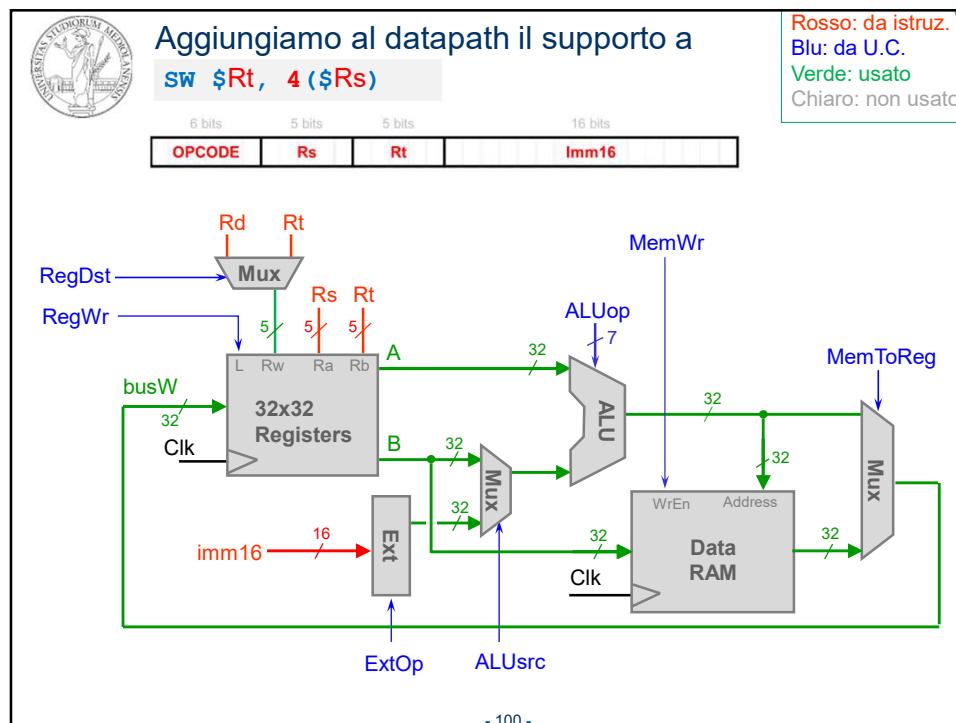

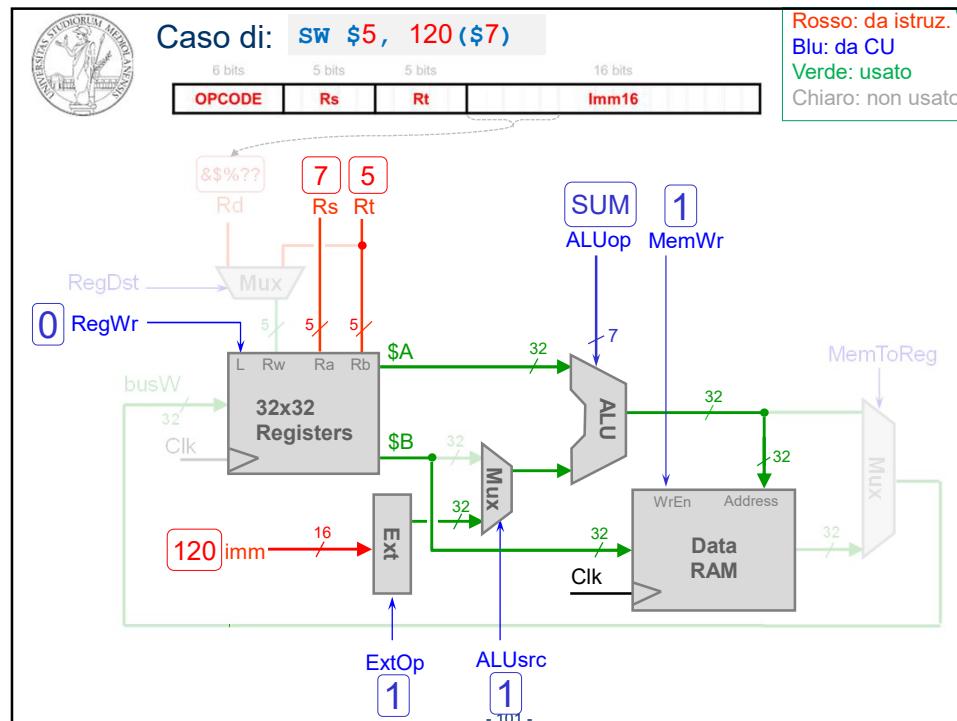

## Prossimo esempio di istruzione MIPS: la store (copia da un registro alla RAM)

Tradotta in assembly MIPS: **SW \$5, (\$14)**

A parole: « *Memorizza il Registro 5 in memoria RAM all'indirizzo contenuto nel Registro 14* »

- 97 -

97

Nota: anche le store hanno l'offset

Tradotta in assembly MIPS: **SW \$5, 4(\$14)**

A parole: « *Memorizza il Registro 5 in memoria RAM all'indirizzo contenuto nel Registro 14... aumentato di 4 bytes* »

Architettura degli elaboratori I - CPU a ciclo singolo

- 98 -

98

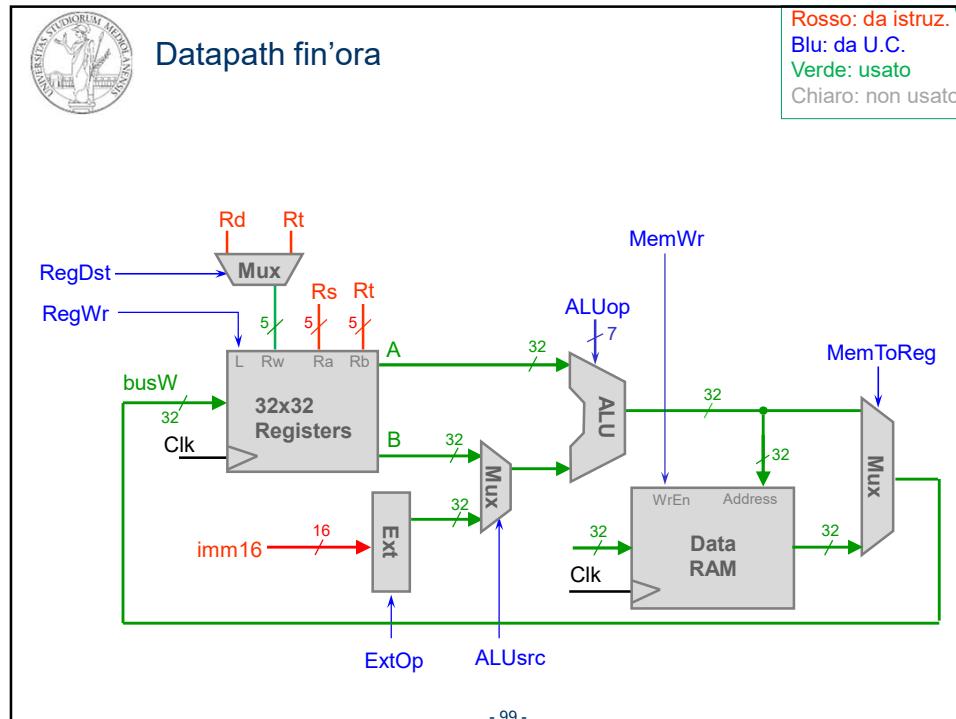

99

100

101

102

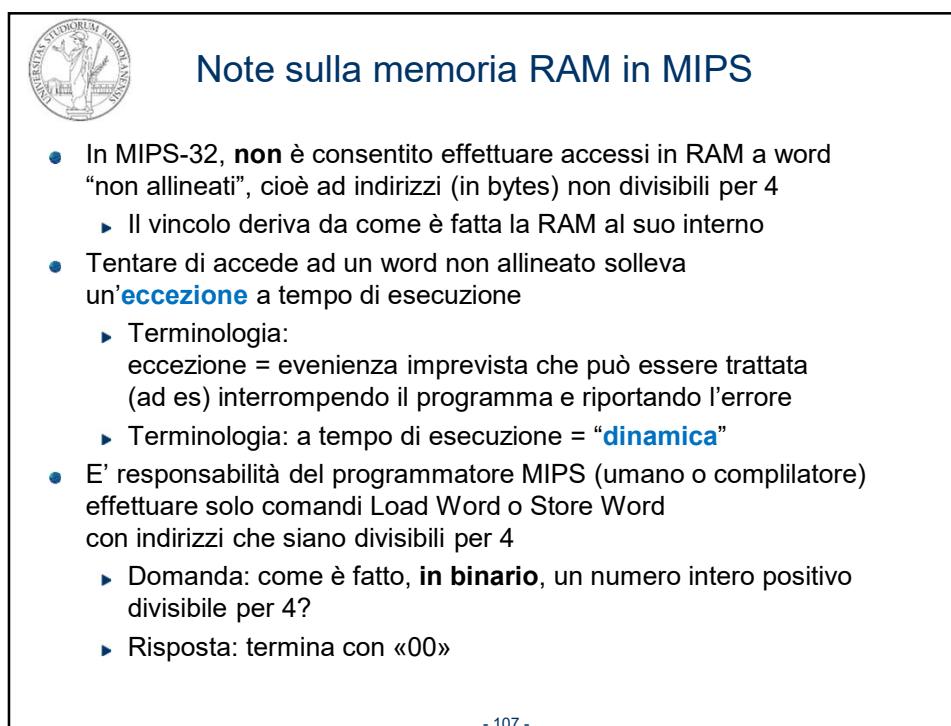

## Accesso alla memoria RAM

- Le modalità di accesso alla RAM sono una delle scelte dell'ISA

- ISA diversi compiono scelte diverse

- Diversi compromessi fra flessibilità, efficienza, facilità di realizzazione...

- Vediamo nei prossimi lucidi i dettagli dell'accesso in memoria del **MIPS-32**

- Eccone un sommario:

- L'indirizzo è di 32 bit (spazio di indirizzamento: da 0 a  $2^{32}-1$ )

- Si accede sempre utilizzando l'indirizzo di un **byte**

- Un accesso legge o scrive un **word** di **4 byte**

- Gli accessi ai word devono essere «**allineati**» (vedi poi)

- L'architettura è «**big-endian**»

- (Vedremo nella prossima lezione: è anche possibile accedere ai singoli byte o a coppie di byte, invece che a parole di quattro byte)

- Tutto quanto sopra si sia applica sia alle letture (load) sia alle scritture (store) in RAM

- 103 -

103

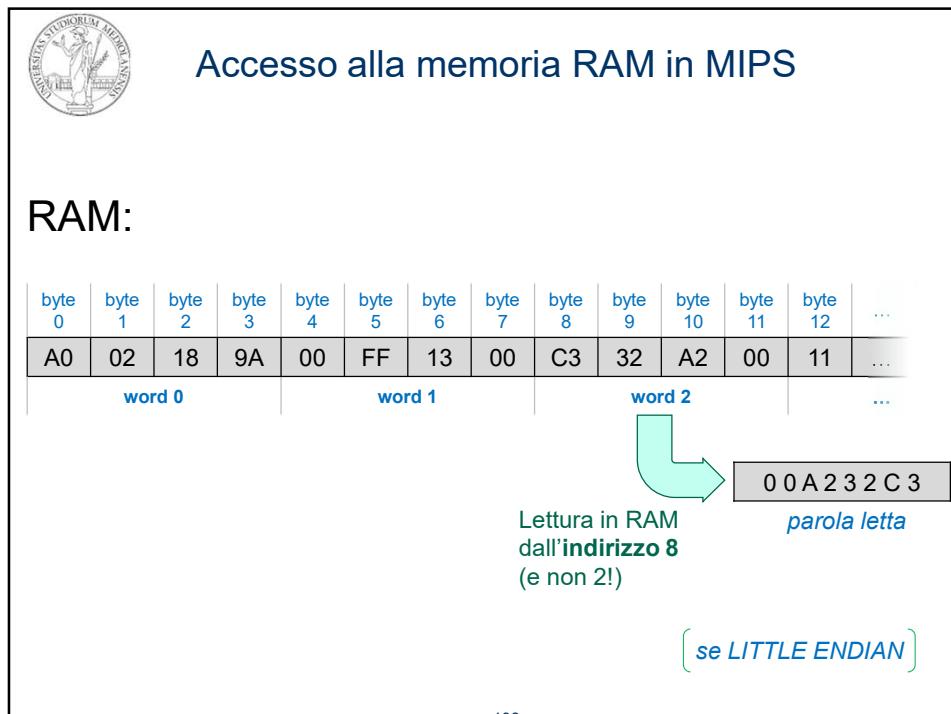

## Accesso alla memoria RAM in MIPS

**RAM:**

|        |        |        |        |        |        |        |        |        |        |         |         |         |     |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------|---------|---------|-----|

| byte 0 | byte 1 | byte 2 | byte 3 | byte 4 | byte 5 | byte 6 | byte 7 | byte 8 | byte 9 | byte 10 | byte 11 | byte 12 | ... |

| A0     | 02     | 18     | 9A     | 00     | FF     | 13     | 00     | C3     | 32     | A2      | 00      | 11      | ... |

word 0                          word 1                          word 2

Lettura in RAM

dall'**indirizzo 8**

(e non 2!)

C 3 3 2 A 2 0 0

*parola letta*

[ se **BIG ENDIAN** ]

- 105 -

105

106

107

108

109

- 109 -

## Programmi in assembly che salvano o leggono dati in RAM

- La memoria che accediamo in lettura e scrittura con load e store è quella che contiene i dati del nostro programma (non il codice)

- Scelta: quale locazione di RAM vogliamo usare per i dati?

- Per rispondere a questa e molte altre) durante la stesura di programmi, usiamo delle **convenzioni**

- ▶ Seguire le convenzioni ha molta utilità: ad esempio, consente a nostri programmi scritti in assembly di interagire correttamente con altri programmi (librerie), e col sistema operativo, perché entrambi seguono le stesse convenzioni

- ▶ Queste convenzioni appartengono al livello dell'assembly.

- ▶ I livelli sottostanti (linguaggio macchina, architettura) non devono esserne consapevoli

- Un primo esempio di convenzione decide per noi dove, in memoria (cioè, a quali indirizzi), posizionare il programma (la sequenza di istruzioni), e dove i dati

- 110 -

110

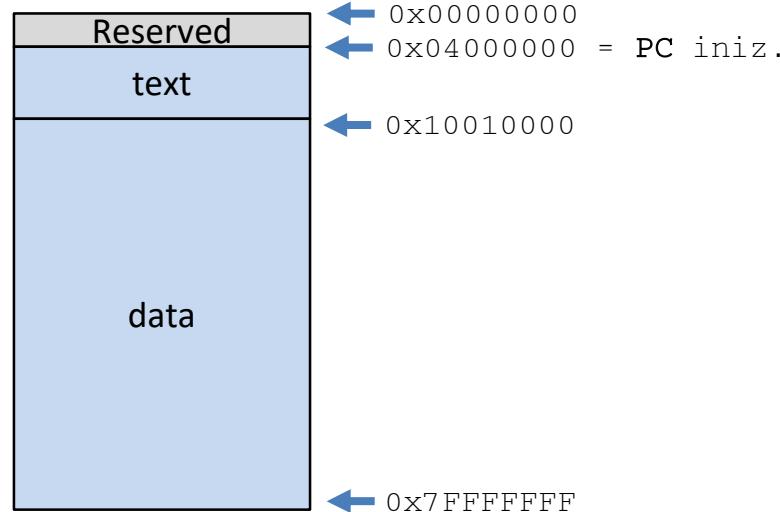

## Convenzione MIPS: partizione della memoria di aree

111

## Convenzione MIPS: partizione della memoria di aree standard

- Programma (SW):

- ▶ Dati

- ▶ +

- ▶ Istruzioni

- Entrambi risiedono in RAM («architettura di Von Neumann»)

- Convenzione MIPS: dividere la RAM in 2 segmenti, in posizioni fissate:

- ▶ Segmento «**data**» (dati)

- ▶ Segmento «**text**» (istruzioni)

- ▶ C'è anche un terzo segmento «**riservato**» al Sistema Operativo (contiene i dati e istruzioni del SW «sistema operativo», e include ad esempio il codice che viene eseguito per gestire le eccezioni, quando si verificano – non ce ne occupiamo)

- Il **Sistema Operativo**, per eseguire un programma, dopo aver caricato in memoria i suoi dati + istruzioni, posiziona il PC al valore della alla prima riga del segmento “text”

- ▶ (di solito; o in generale, all'istruzione dove comincia il «main»)

- 112 -

112

## Direttive Assembler

- Sono «indicazioni» nei nostri sorgenti in assembly, che «spiegano» all'Assembler su come trattare il codice assembly che le segue

- Sintassi: le direttive sono parole precedute da un punto

- (nota: non hanno corrispondente in linguaggio macchina)

- In MIPSweb tutte le direttive sono visibili sotto *help* → *directives*

113

## Alcune direttive Assembler

**.data** : «caro assembler, di seguito ci sono dati (numerici, etc) da tradurre in binario e memorizzare nel segmento **data** della RAM (uno dopo l'altro)»

- In pratica: precede i dati del nostro software.

- I dati li possiamo specificare come literals, in base 10, 16 (0x...), con segno (in CP2), etc

**.text** : «caro assembler, di seguito ci sono istruzioni (o pseudo-istruzioni) da tradurre in linguaggio macchina e da memorizzare nel segmento **text** della RAM (una dopo l'altra)»

- In pratica: precede il codice del nostro software.

(ricorda: software = codice eseguibile + dati)

114

## Info

- Le slides dopo questa anticipano alcuni dettagli finali sulle load e store che vedremo nella *prossima lezione*

- Sono inclusi in questo file solo per non frammentare l'esposizione delle slides in troppi file

- 115 -

115

## Accessi in memoria di singoli byte o di due byte (half-word)

- Fin'ora, abbiamo visto l'accesso in memoria di word (4 byte)

- Il MIPS-32 supporta anche l'accesso «a granularità più piccola»:

- ▶ **Half** (cioè half-words): 2 byte (16 bit)

- ▶ **Byte**: 8 bits.

- Si usano apposite istruzioni

**«load half»** **«store half»**, **«load byte»** **«store byte»**

- Per semplicità, non vediamo il supporto HW di queste istruzioni

- ▶ Necessarie nel **datapath**, e nel **banco di memoria RAM**

- Info pratiche per l'uso:

- ▶ Le **store** sovrascrivono solo gli 1 o 2 byte richiesti della RAM, lasciando il resto della parola di RAM inalterata

- ▶ Le **load** sovrascrivono sempre *tutto* un registro (di 4 byte)!

Gli 1 o 2 byte letti dalla RAM sono estesi in segno.

O, optionalmente, con zero, se si usano le versione «**unsigned**» della **«load byte»** e **«load half»**

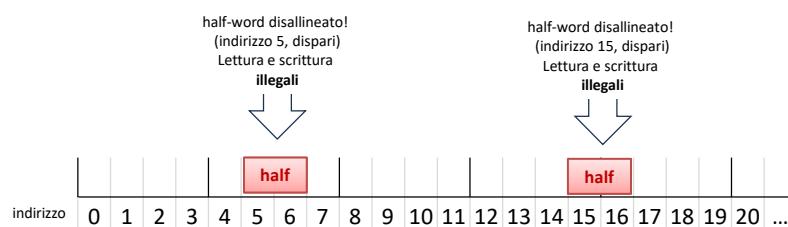

- ▶ Per gli **half**, è richiesto l'allineamento (in load o store) a 2 byte

- 116 -

116

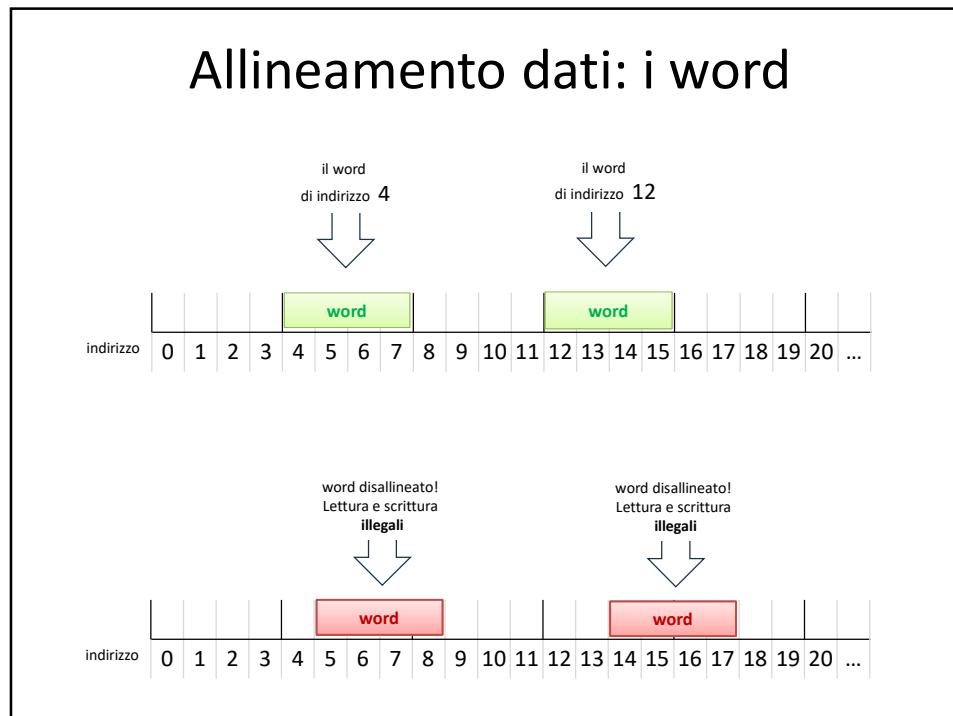

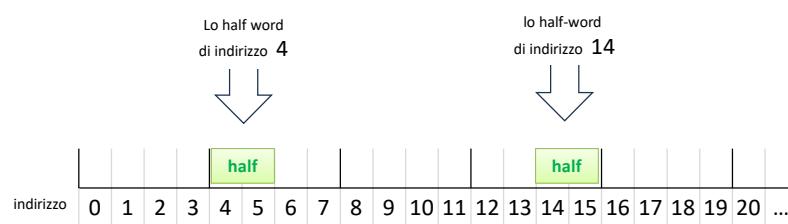

## Allineamento dati: gli half-word

117

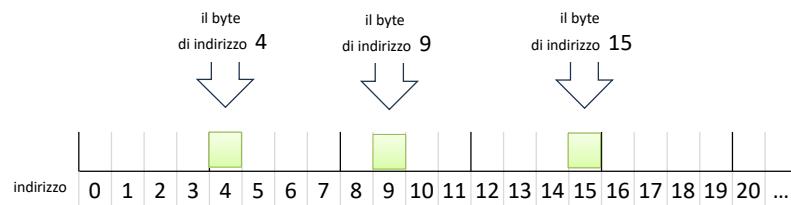

## Allineamento dati: i byte (singoli)

qualsiasi accesso ad un byte è sempre «allineato»

118

### Istruzioni di load e store in assembly MIPS: sommario

| Istruzione                | Sintassi<br>(esempio)   | Semantica<br>(dell'esempio)       | Note                                                        |

|---------------------------|-------------------------|-----------------------------------|-------------------------------------------------------------|

| <b>store word</b>         | <b>sw \$1 150(\$2)</b>  | RAM[ \$2 + 150 ] $\leftarrow$ \$1 | L'offset (in verde) è opzionale e vale 0 se non specificato |

| <b>store half</b>         | <b>sh \$1 150(\$2)</b>  |                                   |                                                             |

| <b>store byte</b>         | <b>sb \$1 150(\$2)</b>  |                                   |                                                             |

| <b>load word</b>          | <b>lw \$1 150(\$2)</b>  |                                   |                                                             |

| <b>load half</b>          | <b>lh \$1 150(\$2)</b>  |                                   |                                                             |

| <b>load byte</b>          | <b>lb \$1 150(\$2)</b>  |                                   |                                                             |

| <b>load half unsigned</b> | <b>lhu \$1 150(\$2)</b> |                                   |                                                             |

| <b>load byte unsigned</b> | <b>lbu \$1 150(\$2)</b> |                                   |                                                             |

119