Lezione 12:

## CPU e linguaggio MIPS

### Parte E: fetch e branch

Marco Tarini

118

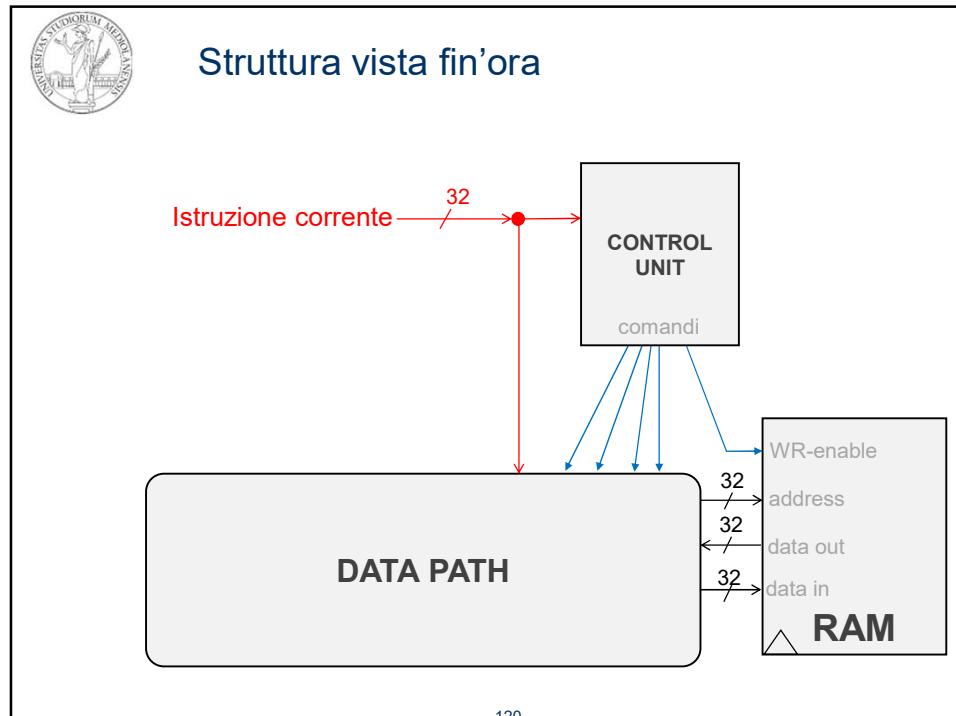

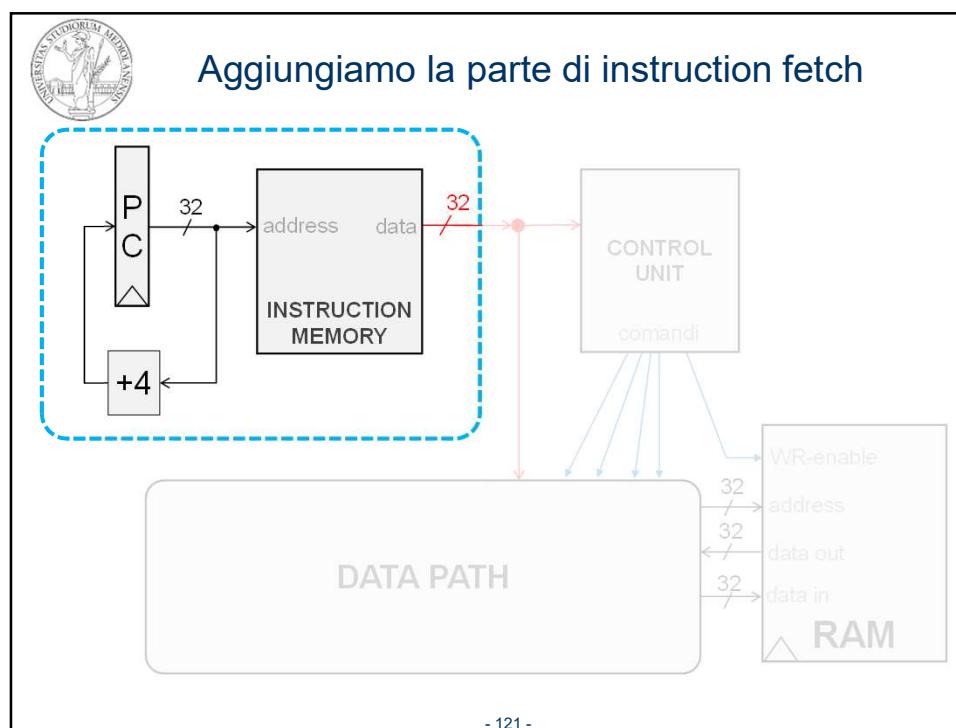

### Next: la parte «fetch» del ciclo «fetch and execute»

- Normalmente, a prescindere da quale istruzione viene eseguita, la CPU deve passare alla istruzione successiva del programma

- ▶ Salvo eccezioni, che vediamo più avanti

- Per far questo bisogna incrementare il Program Counter (PC), cioè il registro che memorizza l'indirizzo in RAM dell'istruzione da leggere

- ▶ Come tutti i registri, il PC assumerà il nuovo valore (cioè quello precedente, ma incrementato), al termine del ciclo di clock (sincronia in scrittura)

- ▶ Questo è parte della fase detta «write back» del ciclo di clock, quella in cui tutti i valori computati nel corrente ciclo sono finalmente memorizzati da una parte o l'altra (RAM, registri, etc)

- Come sappiamo, ogni ciclo di clock inizia con la lettura dell'istruzione corrente dalla memoria, alla locazione contenuta nel PC

- ▶ fase fetch

- 119 -

119

120

121

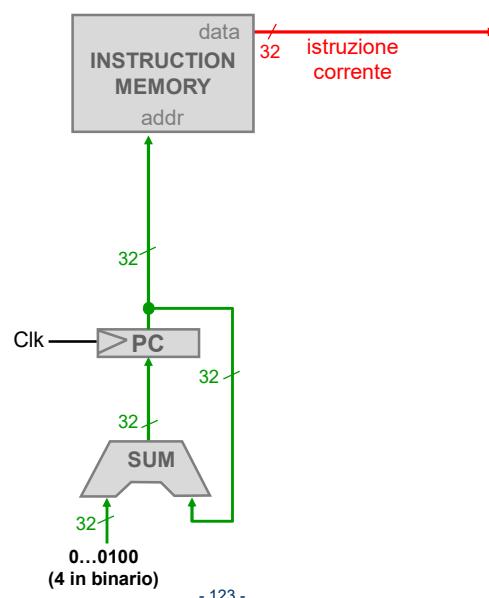

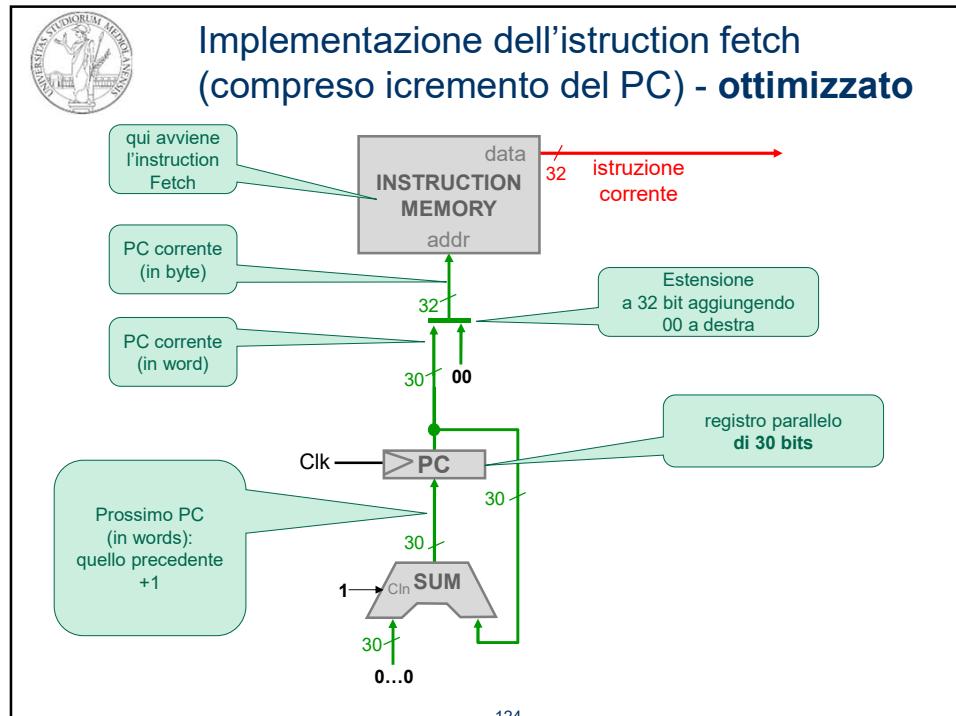

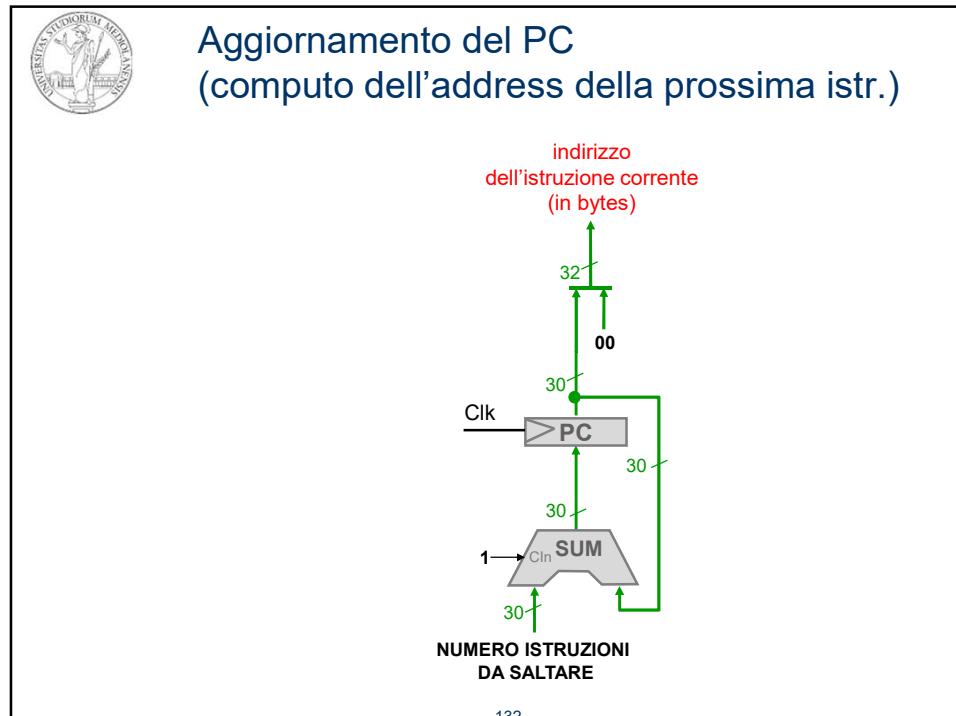

## Il Program Counter (PC)

- **Program Counter** = l'indirizzo dell'istruzione (1word) di cui fare il *fetch*

- ▶ Viene incrementato di 4 byte (1word) al termine di ogni istruzione

- ▶ Il suo incremento determina l'inizio del ciclo successivo (lettura, decodifica ed esecuzione dell'istruzione successiva)

- Il PC è gestito internamente dalla CPU

- ▶ non è **esposto all'utente**: l'utente (il programmatore MIPS) non può leggerlo o scriverlo direttamente;

- ▶ non è necessario che se ne occupi (direttamente)

- Ottimizzazione (scelta progettuale): usiamo un registro PC di soli 30 bit che memorizza i 30 bit più significativi del Program Counter (di 32 bits). Conseguenze:

- ▶ Prima di usare il PC come indirizzo per accedere alla memoria, dovremo appendere due bit 00 a destra, per ottenere l'indirizzo reale (in byte)

- ▶ Per passare all'istruzione successiva, devo incrementare il PC di 1 (e non più di 4) – vantaggioso! [- 122 -](#)

122

## Implementazione dell'istruzione fetch (compreso incremento del PC)

- 123 -

123

124

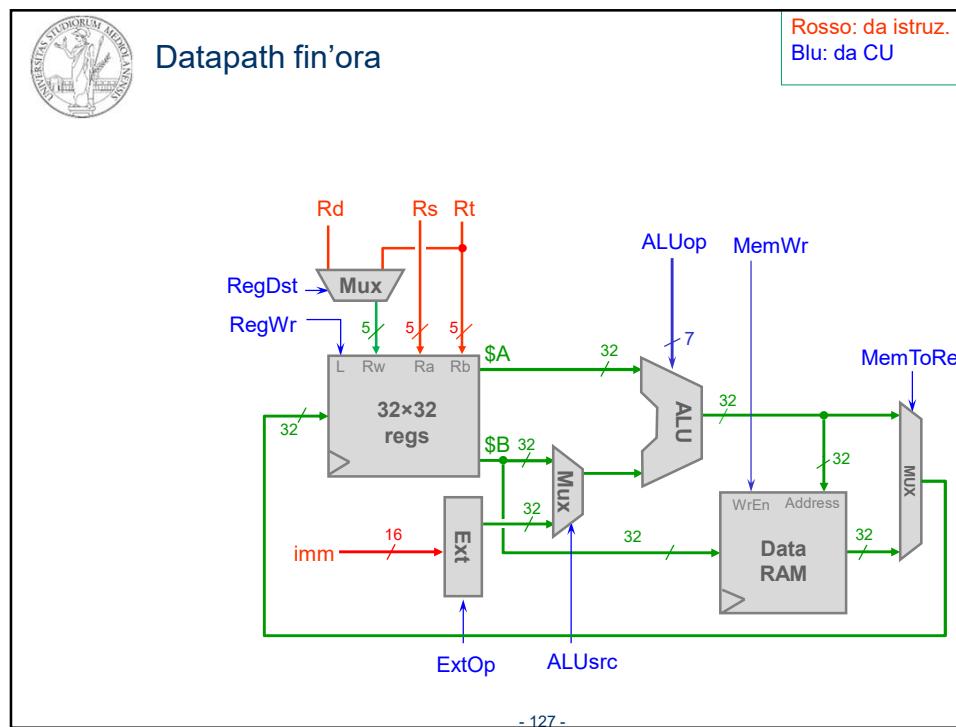

127

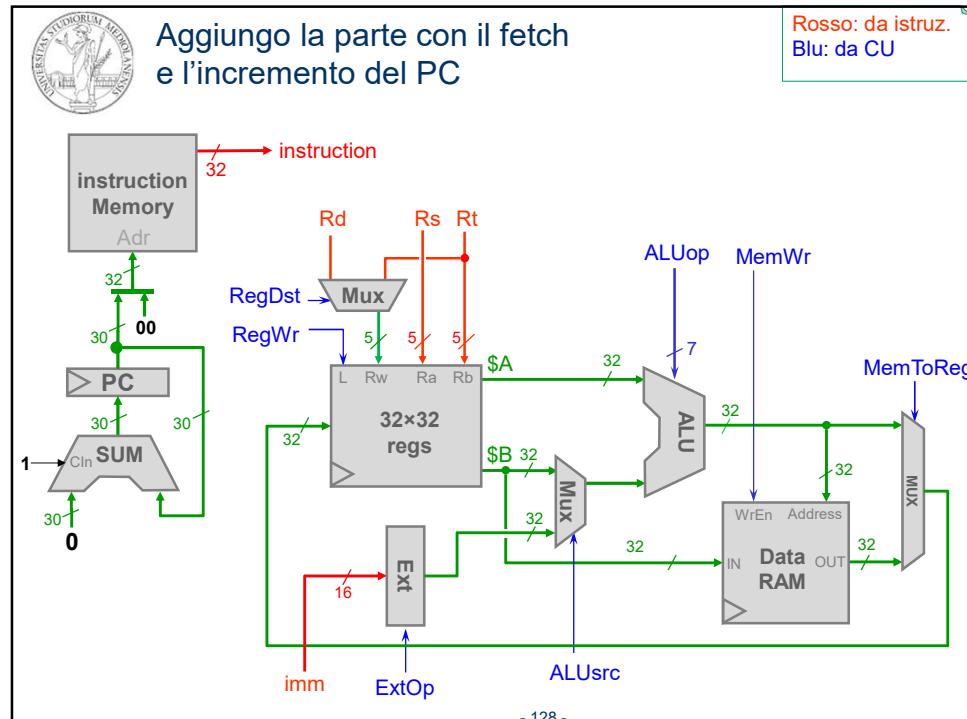

128

## Istruzioni di salto

- Di default, dopo ogni istruzione si passa alla successiva

- ▶ Il PC avanza di 4 bytes

- Le istruzioni di salto fanno eccezione

## Due tipi di istruzioni di salto:

- **Jump** (salto incondizionato)

- ▶ La prossima istruzione è un punto (quasi) arbitrario del codice

- ▶ Il salto viene sempre effettuato

- ▶ Concetto: **go-to** <posizione>

- **Branch** (salto condizionato)

- ▶ Come sopra, ma si salta solo se si verifica una certa condizione

- ▶ La condizione è calcolata dalla ALU paragonando registri

- ▶ Se non si salta, la prossima istruzione è quella successiva a quella corrente (come normale)

- ▶ Concetto: «**if** <qualcosa> **then go-to** <posizione>»

- 129 -

129

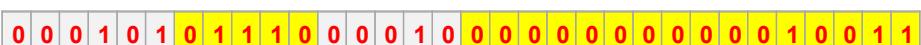

Esempio di Branch in MIPS

|                                                                  |           |           |                            |               |  |  |  |  |  |  |  |  |  |  |  |

|------------------------------------------------------------------|-----------|-----------|----------------------------|---------------|--|--|--|--|--|--|--|--|--|--|--|

| <b>0 0 0 1 0 0 0 1 1 1 0 1 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 1 1</b> |           |           |                            |               |  |  |  |  |  |  |  |  |  |  |  |

| Branch on Equal                                                  | 14        | 16        | 35                         | <i>in CP2</i> |  |  |  |  |  |  |  |  |  |  |  |

| <b>OPCODE</b>                                                    | <b>RS</b> | <b>RT</b> | <b>IMMEDIATE (16 bits)</b> |               |  |  |  |  |  |  |  |  |  |  |  |

Tradotta in assembly MIPS: **BEQ \$14, \$16, 35**

A parole: « *Paragona i valori dei registri 14 e 16: se sono uguali, allora salta 35 istruzioni in avanti (e riparti da quella successiva)* »

- 130 -

130

Esempio di Branch in MIPS

|                                                                    |           |           |                            |               |  |  |  |  |  |  |  |  |  |  |  |

|--------------------------------------------------------------------|-----------|-----------|----------------------------|---------------|--|--|--|--|--|--|--|--|--|--|--|

| <b>0 0 0 1 0 0 0 1 1 1 0 1 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 0 0</b> |           |           |                            |               |  |  |  |  |  |  |  |  |  |  |  |

| Branch on Equal                                                    | 14        | 16        | -4                         | <i>in CP2</i> |  |  |  |  |  |  |  |  |  |  |  |

| <b>OPCODE</b>                                                      | <b>RS</b> | <b>RT</b> | <b>IMMEDIATE (16 bits)</b> |               |  |  |  |  |  |  |  |  |  |  |  |

Tradotta in assembly MIPS: **BEQ \$14, \$16, -4**

A parole: « *Paragona i valori dei registri 14 e 16: se sono uguali, allora salta di 4 istruzioni in indietro (e riparti da quella successiva)* »

- 131 -

131

132

133

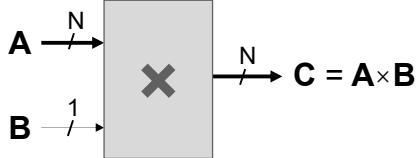

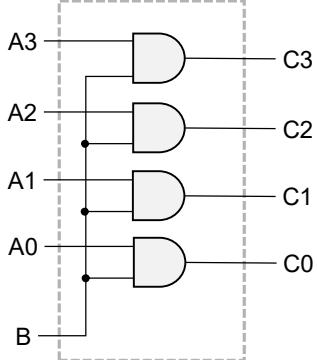

Un blocco funzionale per moltiplicazione...

...quando il secondo termine ha 1 bit 😊

Realizzazione (banale!):

(qui, per  $N = 4$ )

(è un circuito che annulla A quando il bit B vale 0, altrimenti lascia A inalterato in output)

- 134 -

134

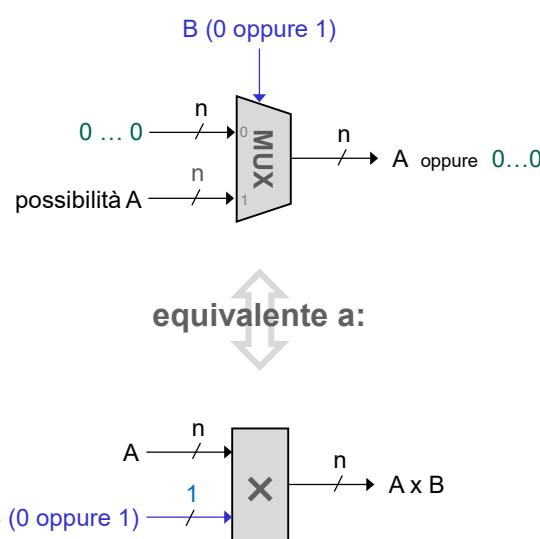

«Moltiplicatori» N per 1

- E' la versione ottimizzata di un MUX a 2 vie quando una delle due alternative è costituita da tutti zero

- 135 -

135

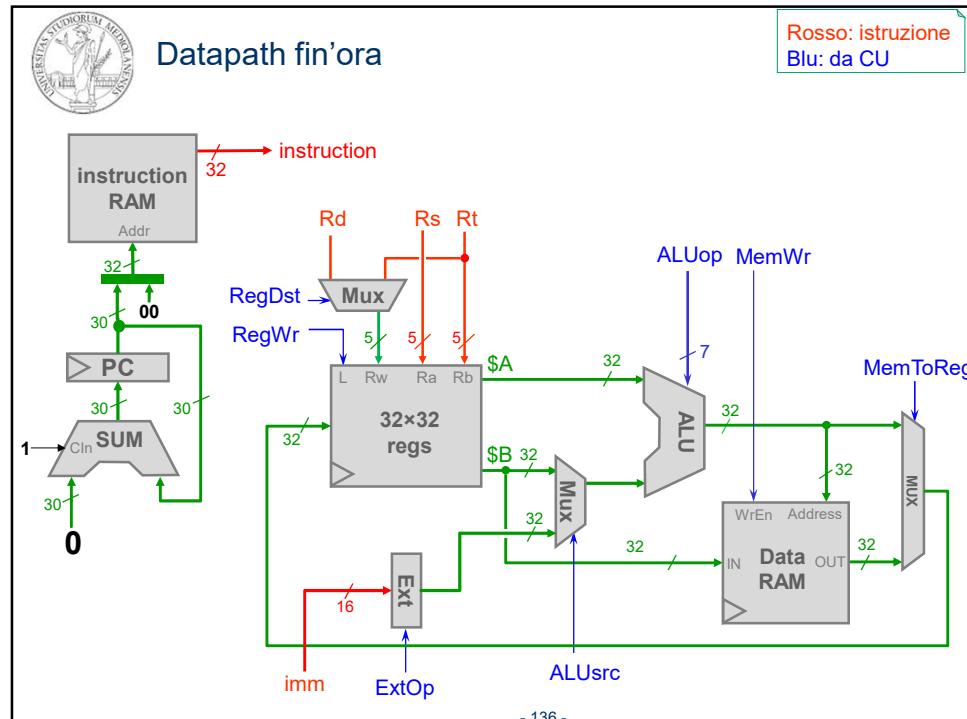

136

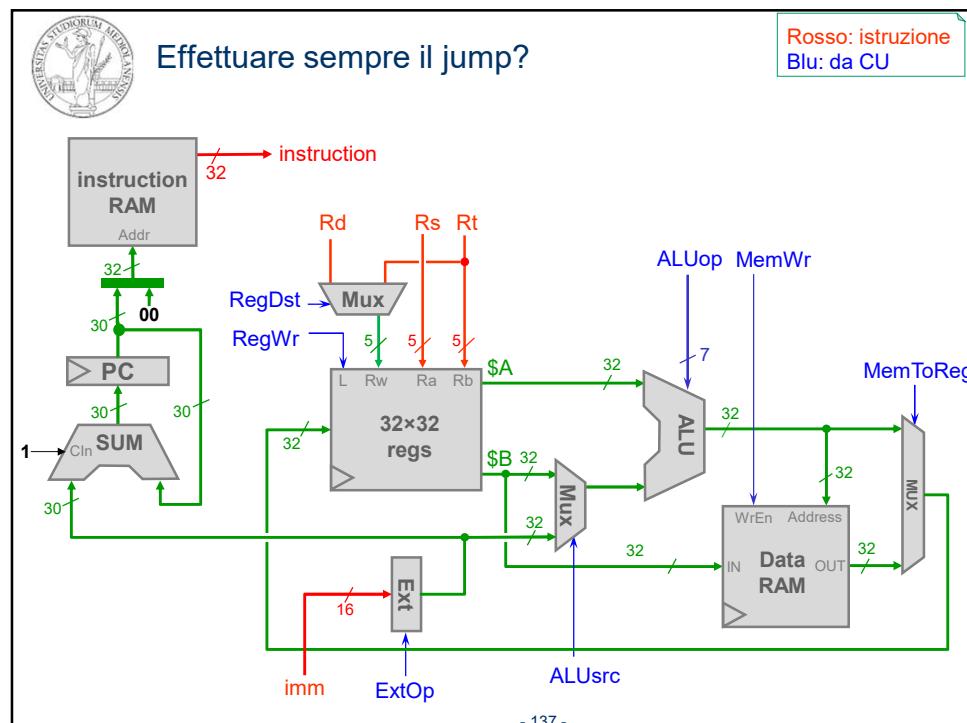

137

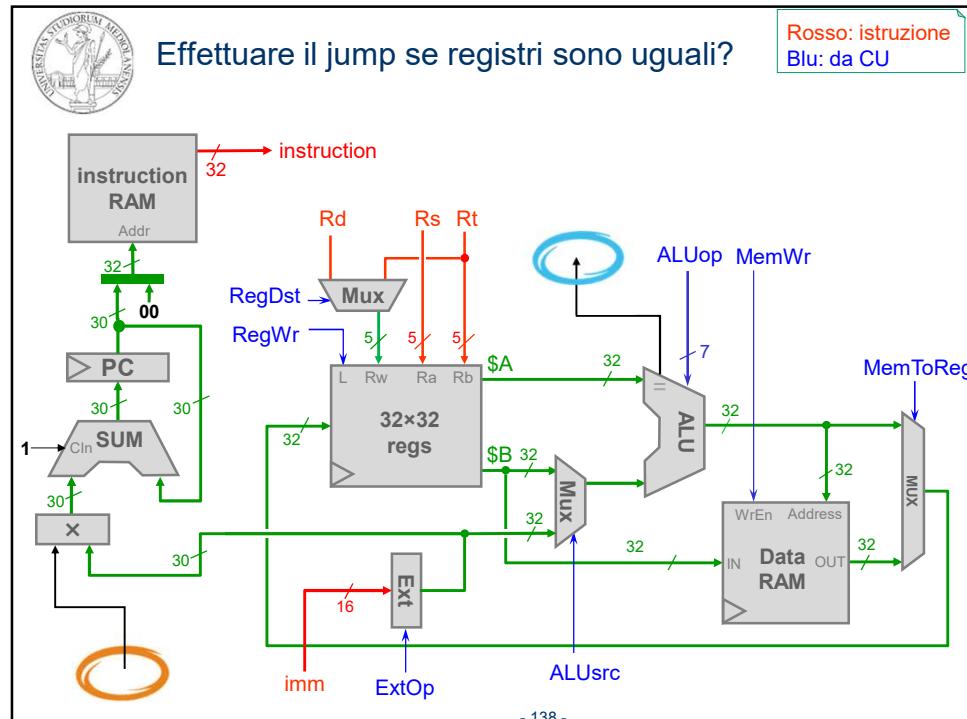

138

139

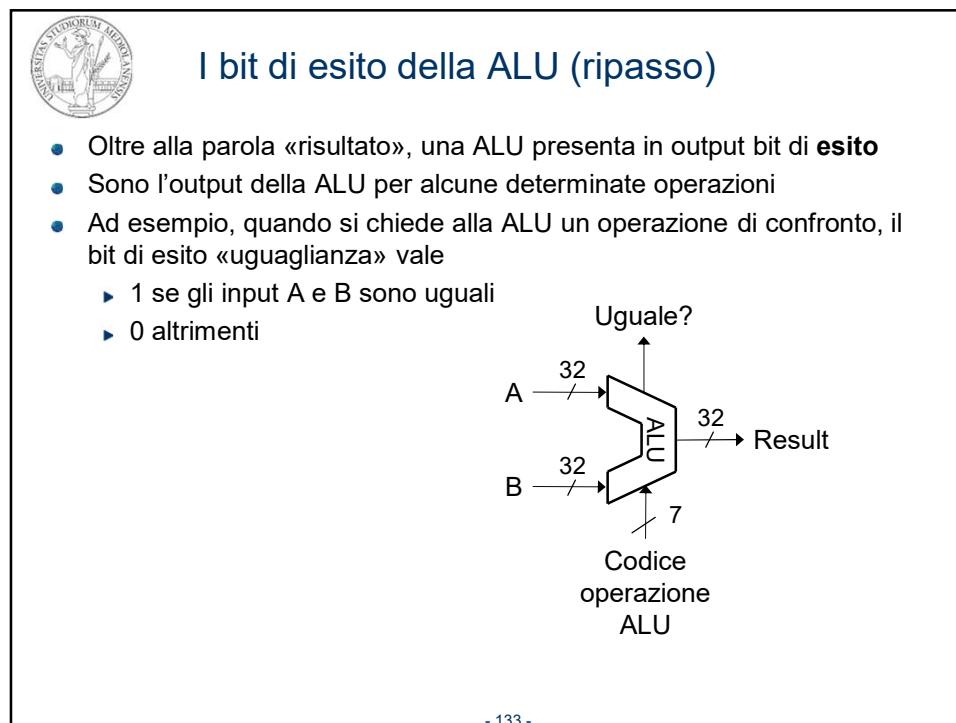

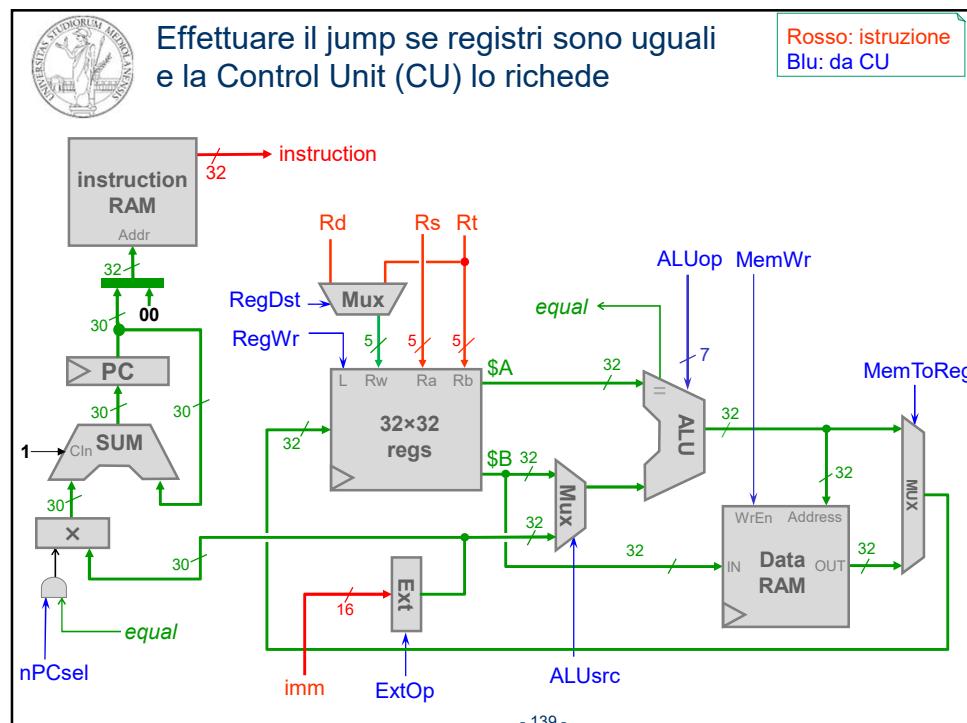

### Implementazione del supporto HW per l'istruzione "branch on equal": note

- Le branch sono istruzioni di tipo «l»

- hanno due campi «registri» che in questo caso identificano gli indici dei due registri da paragonare, e un campo immediate di 16 bit, che in questo caso riporta il numero di istruzioni da saltare

- Il valore immediate, esteso a 32 bit, viene immesso (anche) come addendo nell'addizionatore che incrementa il PC

- L'estensione, in questo caso, è IN SEGNO, perché il numero di istruzioni da saltare è espresso in CP2 (può essere neg o pos)

- Dopo l'estensione vanno anche decurtati i due bit più significativi (lasciandone solo 30), perché il nostro PC è di 30 bit

- Questo valore di incremento del PC viene però azzerato se l'**esito** "uguaglianza" dalla ALU (che paragona i due registri \$rs e \$rt) vale 0

- In questo caso, il PC viene incrementato solo di 1 (attraverso cin)

- L'esito viene messo in AND con un apposito comando di controllo della Control Unit, **nPCsel** (next PC selector) che se vale 0 annulla il salto

- questo comando vale 1 solo nelle istruzioni di branch

- 140 -

140

### Altra pseudo-istruzione MIPS di branch (già supportata dall'HW visto)

|                       |   |   |   |   |    |   |   |   |    |   |   |   |   |   |   |   |   |   |   |                     |   |   |   |   |   |        |   |

|-----------------------|---|---|---|---|----|---|---|---|----|---|---|---|---|---|---|---|---|---|---|---------------------|---|---|---|---|---|--------|---|

| 0                     | 0 | 0 | 1 | 0 | 0  | 0 | 1 | 1 | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0                   | 0 | 0 | 0 | 1 | 0 | 0      | 1 |

| Branch<br>on<br>equal |   |   |   |   | 14 |   |   |   | 0  |   |   |   |   |   |   |   |   |   |   | 35                  |   |   |   |   |   | in CP2 |   |

| OPCODE                |   |   |   |   | RS |   |   |   | RT |   |   |   |   |   |   |   |   |   |   | IMMEDIATE (16 bits) |   |   |   |   |   |        |   |

Tradotta in assembly MIPS: **BEQ \$14, \$0, 35**

oppure: **BEQZ \$14, 35**

A parole: « *Se il valore del registro 14 è proprio 0, allora salta in avanti di 35 istruzioni* »

- 141 -

141

| Significato lettera per lettera delle istruzioni assembly di branch |                                     |

|---------------------------------------------------------------------|-------------------------------------|

| <b>bgez</b>                                                         |                                     |

| <b>ge</b>                                                           | greater or equal $\geq$             |

| <b>gt</b>                                                           | greater than $>$                    |

| <b>b</b> branch on                                                  | <b>le</b> less than or equal $\leq$ |

|                                                                     | <b>lt</b> less than $<$             |

|                                                                     | <b>eq</b> equal $\equiv$            |

|                                                                     | <b>ne</b> not equal $\neq$          |

| <small>- 142 -</small>                                              |                                     |

142

| Altra istruzione MIPS di branch                                                                               |           |           |                            |               |  |  |

|---------------------------------------------------------------------------------------------------------------|-----------|-----------|----------------------------|---------------|--|--|

|                           |           |           |                            |               |  |  |

| Branch<br>on<br>not equal                                                                                     | 14        | 2         | 35                         | <i>in CP2</i> |  |  |

| <b>OPCODE</b>                                                                                                 | <b>RS</b> | <b>RT</b> | <b>IMMEDIATE (16 bits)</b> |               |  |  |

| Tradotta in assembly MIPS: <b>BNE \$14, \$2, 35</b>                                                           |           |           |                            |               |  |  |

| A parole: « <i>Se i registri 14 e 2 non hanno lo stesso valore, allora salta in avanti di 35 istruzioni</i> » |           |           |                            |               |  |  |

| <small>- 143 -</small>                                                                                        |           |           |                            |               |  |  |

143

**Altra istruzione MIPS di branch**

|                                                           |           |                      |                            |        |  |  |  |  |  |  |  |  |  |  |  |

|-----------------------------------------------------------|-----------|----------------------|----------------------------|--------|--|--|--|--|--|--|--|--|--|--|--|

| 0 0 0 0 0 1 0 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 1 1 |           |                      |                            |        |  |  |  |  |  |  |  |  |  |  |  |

| Branch<br>on...                                           | 14        | ...less<br>than zero | 35                         | in CP2 |  |  |  |  |  |  |  |  |  |  |  |

| <b>OPCODE</b>                                             | <b>RS</b> | <b>RT</b>            | <b>IMMEDIATE (16 bits)</b> |        |  |  |  |  |  |  |  |  |  |  |  |

Tradotta in assembly MIPS: **BLTZ \$14, 35**

A parole: « *Se il registro 14 è strettamente negativo ( $< 0$ ), allora salta in avanti di 35 istruzioni* »

- 144 -

144

**Altra istruzione MIPS di branch**

|                                                             |           |                                     |                            |        |  |  |  |  |  |  |  |  |  |  |  |

|-------------------------------------------------------------|-----------|-------------------------------------|----------------------------|--------|--|--|--|--|--|--|--|--|--|--|--|

| 0 0 0 0 0 1 0 1 1 1 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 1 0 0 1 1 |           |                                     |                            |        |  |  |  |  |  |  |  |  |  |  |  |

| Branch<br>on...                                             | 14        | ...greater<br>or equal<br>than zero | 35                         | in CP2 |  |  |  |  |  |  |  |  |  |  |  |

| <b>OPCODE</b>                                               | <b>RS</b> | <b>RT</b>                           | <b>IMMEDIATE (16 bits)</b> |        |  |  |  |  |  |  |  |  |  |  |  |

Tradotta in assembly MIPS: **BGEZ \$14, 35**

A parole: « *Se il registro 14 è positivo ( $\geq 0$ ), allora salta in avanti di 35 istruzioni* »

- 145 -

145

## Alcune istruzioni di Branch in assembly MIPS

- Con confronto fra due registri

|                          |                            |             |

|--------------------------|----------------------------|-------------|

| <b>beq</b> \$ra \$rb +20 | branch on <i>equal</i>     | \$ra = \$rb |

| <b>bne</b> \$ra \$rb -3  | branch on <i>not equal</i> | \$ra ≠ \$rb |

| <b>blt</b> \$ra \$rb +5  | branch on <i>less then</i> | \$ra < \$rb |

- Con confronto fra registro e zero

|                      |                                           |          |

|----------------------|-------------------------------------------|----------|

| <b>bgez</b> \$ra +20 | branch on<br><i>greater-or-equal zero</i> | \$ra ≥ 0 |

| <b>bgtz</b> \$ra +6  | branch on<br><i>greater-than zero</i>     | \$ra > 0 |

| <b>blez</b> \$ra 7   | branch on<br><i>less-or-equal to zero</i> | \$ra ≤ 0 |

| <b>bltz</b> \$ra 30  | branch on<br><i>less-than zero</i>        | \$ra < 0 |

146

## Domande ed esercizi

- Quale valore numerico “immediate” deve presentare una istruzione di branch per saltare a... se stessa?

- Cosa succede all'esecuzione del programma, se il salto viene effettuato?

- Mettiti nei panni della CU e decidi ciascuno dei comandi inviare al datapath per effettuare una istruzione BEQ

- Quante istruzioni si possono saltare, al massimo, in avanti o indietro, con un comando branch?

- Come mai abbiamo bisogno di un addizionatore separato per effettuare l'incremento del PC?

Non si potrebbe usare l'addizionatore presente della ALU?

- 147 -

147