185

186

187

188

## L'Istruction Set MIPS

Diagram showing the first six bits of an instruction pointing to the OpCode column and the last six bits pointing to the Funct column.

| Mnemonic     | Meaning                                | Type | OpCode | Funct |

|--------------|----------------------------------------|------|--------|-------|

| <b>add</b>   | Add                                    | R    | 0x00   | 0x20  |

| <b>addu</b>  | Add Unsigned                           | R    | 0x00   | 0x21  |

| <b>and</b>   | Bitwise AND                            | R    | 0x00   | 0x24  |

| <b>div</b>   | Divide                                 | R    | 0x00   | 0x1A  |

| <b>divu</b>  | Unsigned Divide                        | R    | 0x00   | 0x1B  |

| <b>jr</b>    | Jump to Address in Register            | R    | 0x00   | 0x08  |

| <b>mfhi</b>  | Move from HI Register                  | R    | 0x00   | 0x10  |

| <b>mthi</b>  | Move to HI Register                    | R    | 0x00   | 0x11  |

| <b>mflo</b>  | Move from LO Register                  | R    | 0x00   | 0x12  |

| <b>mtlo</b>  | Move to LO Register                    | R    | 0x00   | 0x13  |

| <b>mult</b>  | Multiply                               | R    | 0x00   | 0x18  |

| <b>multu</b> | Unsigned Multiply                      | R    | 0x00   | 0x19  |

| <b>nor</b>   | Bitwise NOR (NOT-OR)                   | R    | 0x00   | 0x27  |

| <b>xor</b>   | Bitwise XOR (Exclusive-OR)             | R    | 0x00   | 0x26  |

| <b>or</b>    | Bitwise OR                             | R    | 0x00   | 0x25  |

| <b>slt</b>   | Set to 1 if Less Than                  | R    | 0x00   | 0x2A  |

| <b>sltu</b>  | Set to 1 if Less Than Unsigned         | R    | 0x00   | 0x2B  |

| <b>sll</b>   | Logical Shift Left                     | R    | 0x00   | 0x00  |

| <b>srl</b>   | Logical Shift Right (0-extended)       | R    | 0x00   | 0x02  |

| <b>sra</b>   | Arithmetic Shift Right (sign-extended) | R    | 0x00   | 0x03  |

| <b>sub</b>   | Subtract                               | R    | 0x00   | 0x22  |

189

|              |                                          |   |      |      |

|--------------|------------------------------------------|---|------|------|

| <b>subu</b>  | Unsigned Subtract                        | R | 0x00 | 0x23 |

| <b>slti</b>  | Set to 1 if Less Than Immediate          | I | 0x0A | NA   |

| <b>sltiu</b> | Set to 1 if Less Than Unsigned Immediate | I | 0x0B | NA   |

| <b>andi</b>  | Bitwise AND Immediate                    | I | 0x0C | NA   |

| <b>ori</b>   | Bitwise OR Immediate                     | I | 0x0D | NA   |

| <b>lui</b>   | Load Upper Immediate                     | I | 0x0F | NA   |

| <b>j</b>     | Jump to Address                          | J | 0x02 | NA   |

| <b>sw</b>    | Store Word                               | I | 0x2B | NA   |

| <b>jal</b>   | Jump and Link                            | J | 0x03 | NA   |

| <b>beq</b>   | Branch if Equal                          | I | 0x04 | NA   |

| <b>bne</b>   | Branch if Not Equal                      | I | 0x05 | NA   |

| <b>blez</b>  | Branch if Less Than or Equal to Zero     | I | 0x06 | NA   |

| <b>bgtz</b>  | Branch on Greater Than Zero              | I | 0x07 | NA   |

| <b>addi</b>  | Add Immediate                            | I | 0x08 | NA   |

| <b>addiu</b> | Add Unsigned Immediate                   | I | 0x09 | NA   |

| <b>mfc0</b>  | Move from Coprocessor 0                  | I | 0x10 | NA   |

| <b>lb</b>    | Load Byte                                | I | 0x20 | NA   |

| <b>lw</b>    | Load Word                                | I | 0x23 | NA   |

| <b>lbu</b>   | Load Byte Unsigned                       | I | 0x24 | NA   |

| <b>lhu</b>   | Load Halfword Unsigned                   | I | 0x25 | NA   |

| <b>sb</b>    | Store Byte                               | I | 0x28 | NA   |

| <b>sh</b>    | Store Halfword                           | I | 0x29 | NA   |

(non abbiamo visto tutte le istruzioni di questa lista)

(il nostro DataPath non le supporta tutte)

- 190 -

190

- 191 -

191

- 192 -

192

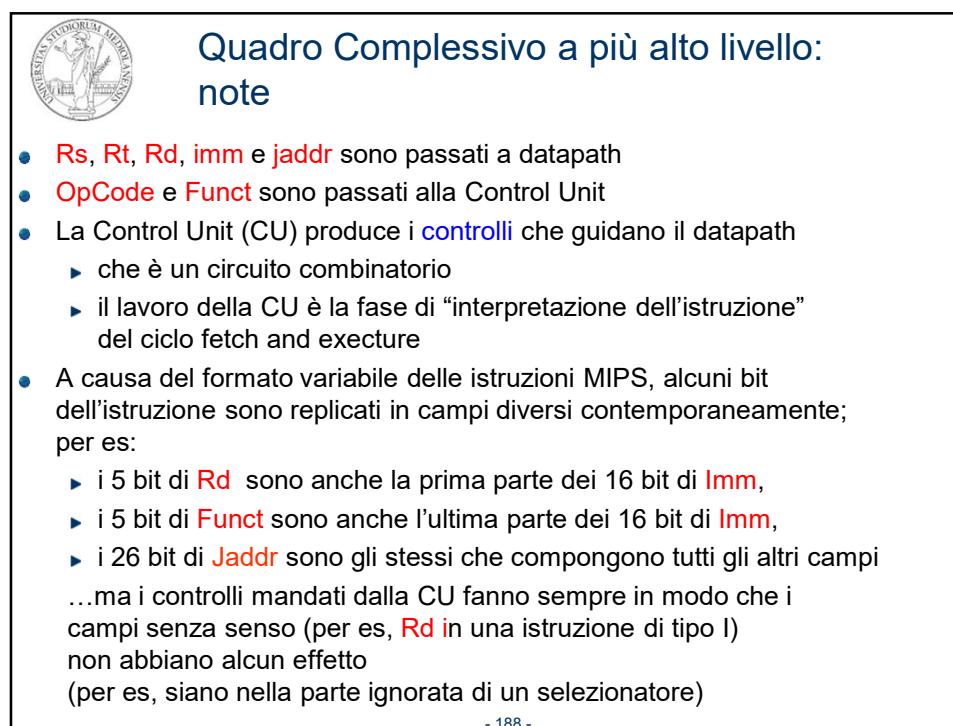

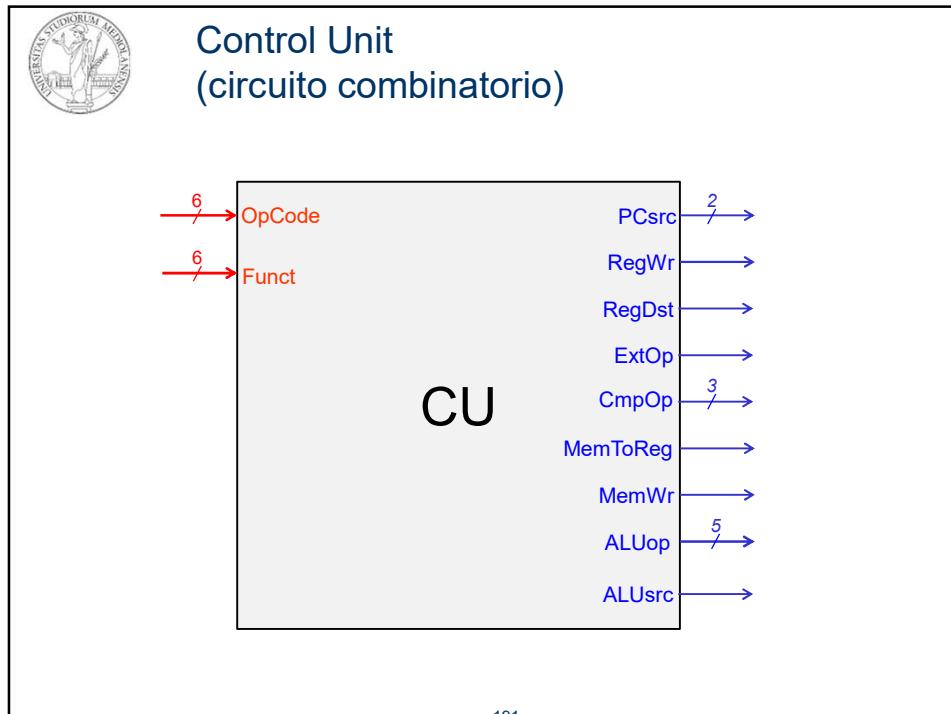

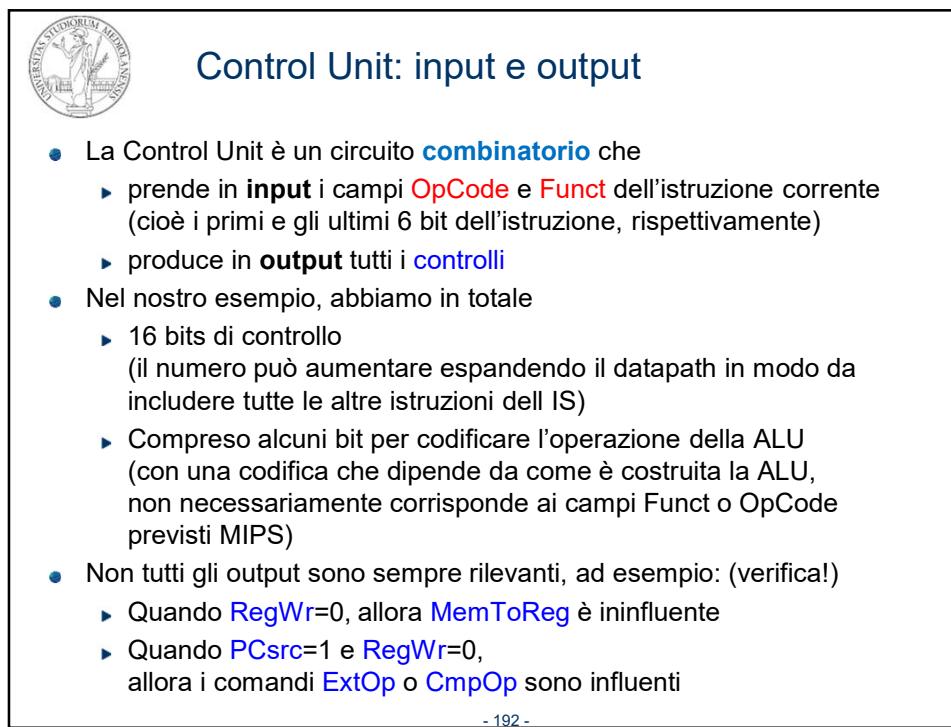

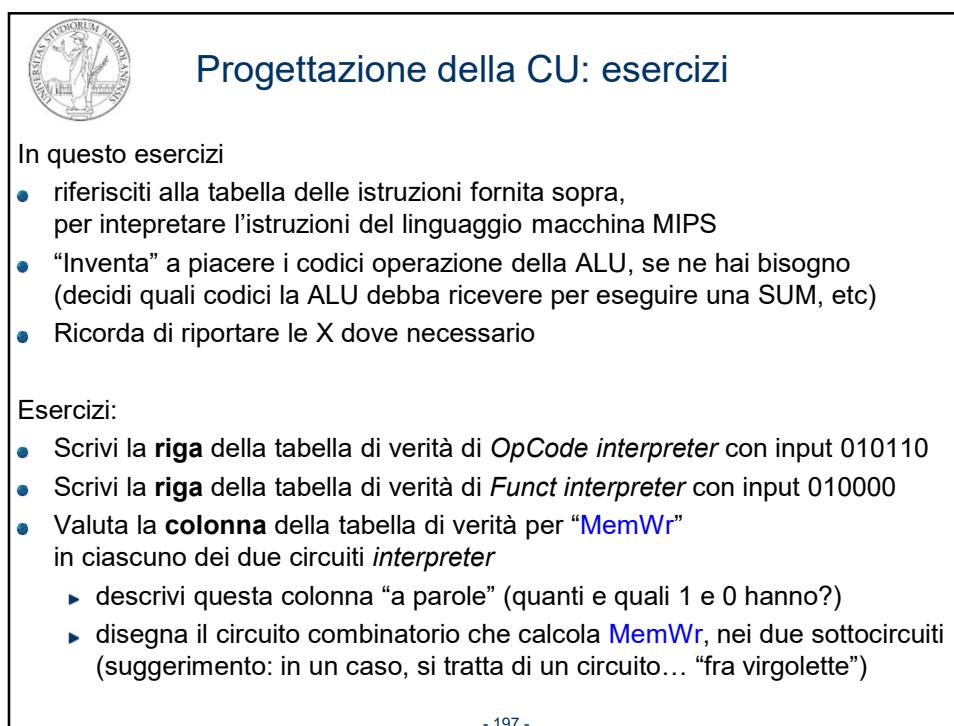

## Control Unit: progettazione

- Per progettare questo circuito, potremmo procedere come per qualsiasi circuito combinatorio, cioè «semplicemente» ...

- ▶ Scrivere la sua (lunga) tabella delle verità

- ▶ Ogni sua riga corrisponde ad un tipo di istruzione (vedi tabella) e quindi ad un valore per ogni bit di controllo

- ▶ Nota: questa tabella riporta anche i valori ininfluenti, come delle «X» («don't care»)

- ▶ Trasformarla in un circuito, come abbiamo imparato (per es, tramite 1ma forma normale, come Somma di Prodotti)

- Nel nostro esempio, questa tabella avrebbe

- ▶  $2^{12} = 4096$  righe

- ▶ 16 colonne di output

- Non è impossibile procedere in questo modo, ma c'è un modo più pratico...

- 193 -

193

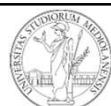

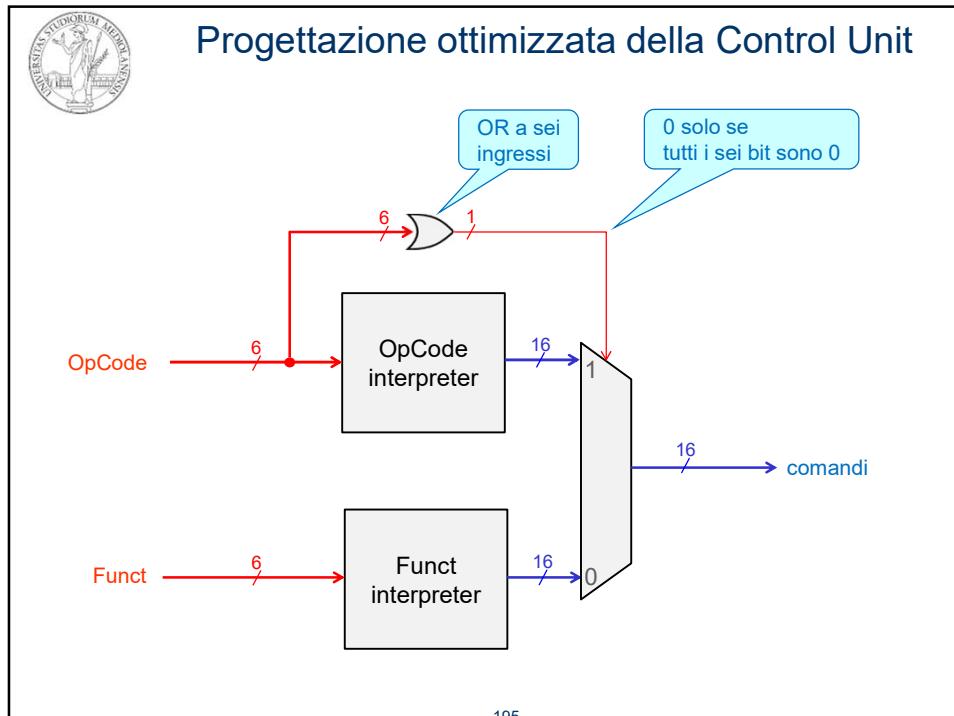

## Control Unit: progettazione ottimizzata

- Come semplificazione, notiamo che le istruzioni si dividono in due gruppi:

- Istruzioni R

- ▶ cioè tutte le operazioni fra registri (e anche `jr`, `mfhi`, e poche altre)

- ▶ Hanno tutte **OpCode = 000000**

- ▶ L'output della CU dipende solo da **Funct**

- ▶ Molti output sono costanti, per es, `MemWr = 0`

- Tutte le altre

- ▶ Compresa: operazioni con immediate, le branch, le load, le store, ...

- ▶ Hanno **OpCode ≠ 000000**

- ▶ L'output della CU dipende solo da **OpCode**

- ▶ il campo **Funct**, infatti, non è valido (è... parte di `imm` o di `jaddr`)

- Questa osservazione ci consente di dividere la CU in due sotto circuiti separati, ciascuno assai più semplice (tabella di, al max,  $2^6 = 64$  righe)...

- ▶ non è un caso: MIPS-32 è un ISA progettato con molta attenzione alla semplicità di implementazione HW

- 194 -

194

195

197