Lezione 12:

## CPU e linguaggio MIPS

### Parte I: Considerazioni finali

Marco Tarini

192

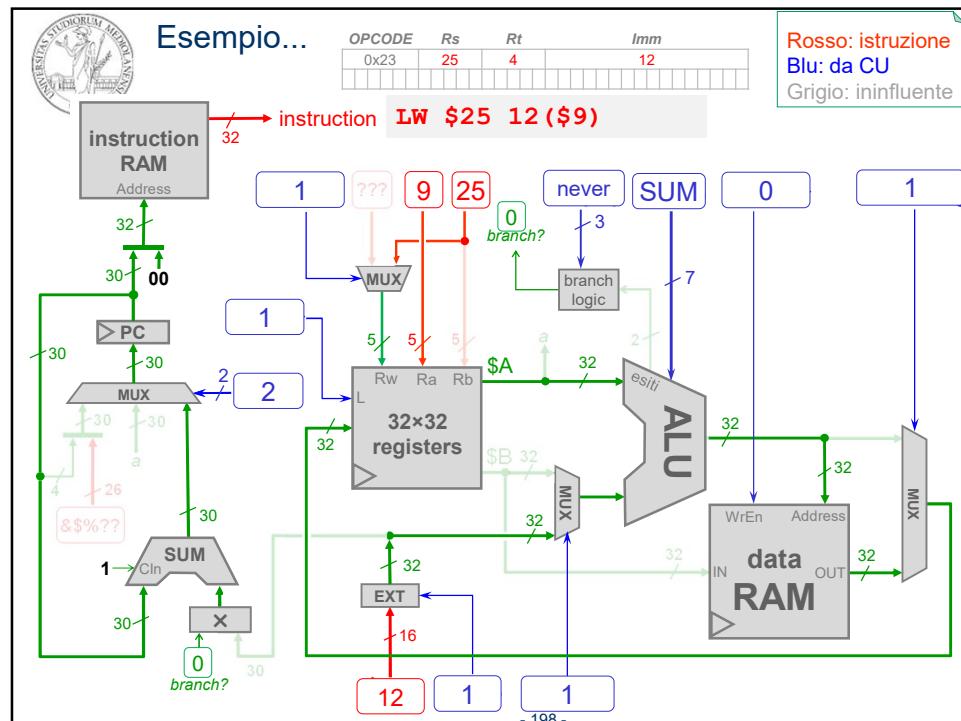

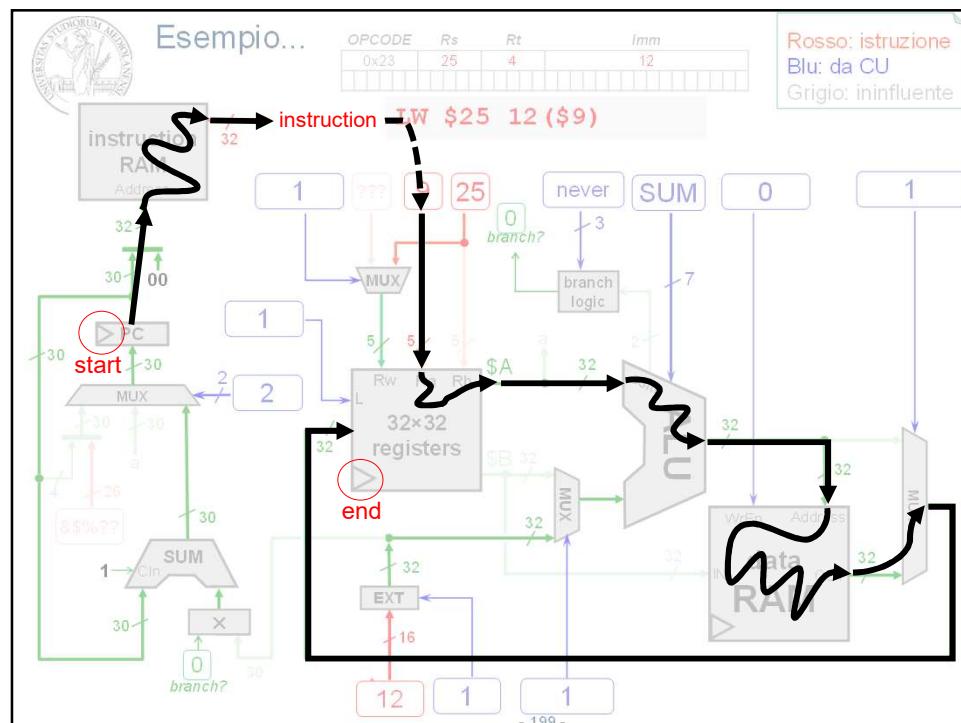

## Datapath e ciclo di clock

- Quanto deve essere lungo il periodo di clock?

- ▶ Risposta: abbastanza da permettere all'intero datapath di essere attraversato dal segnale, a partire dall'update PC, in modo da presentare l'input stabile ad ogni elemento che deve memorizzarlo (fase di «write back»)

- ▶ ☺ guai se il ciclo di clock termina prima: l'elemento di memorizzazione registrerà il dato ancora temporaneo, diverso da quello corretto!

- Quali elementi sono coinvolti dalla write-back? Dipende dall'istruzione:

- ▶ Il nuovo PC, per tutte le istruzioni, compresi i salti

- ▶ La RAM, solo per le istruzioni di Store

- ▶ Il banco dei registri, per tutte le istruzioni che modificano i registri, comprese: le operazioni ALU fra registri e/o valori immediati, e le Load dalla RAM

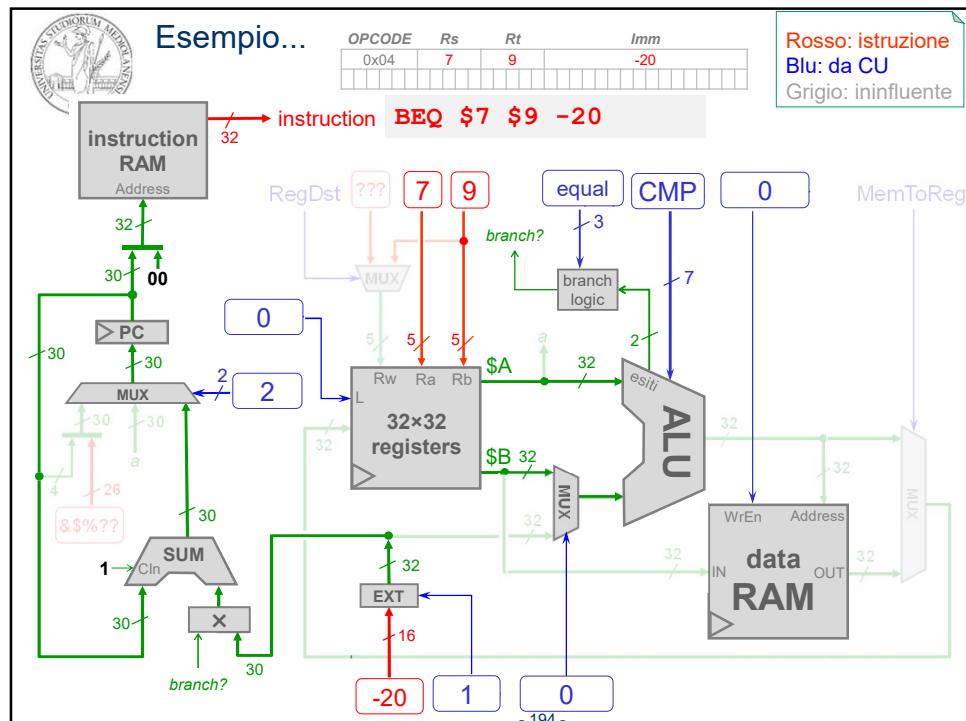

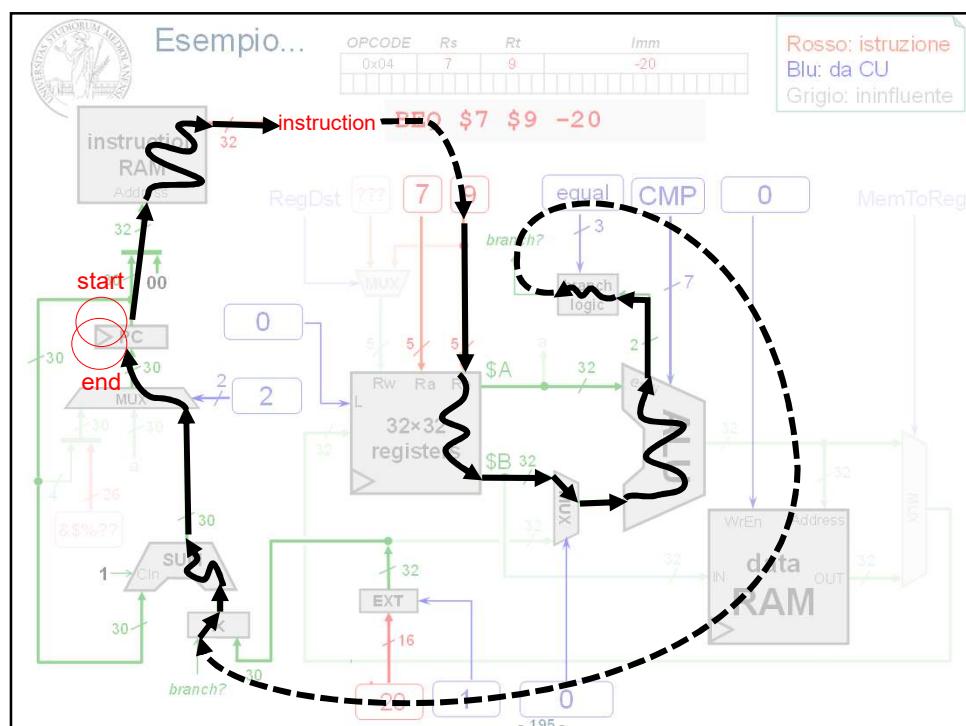

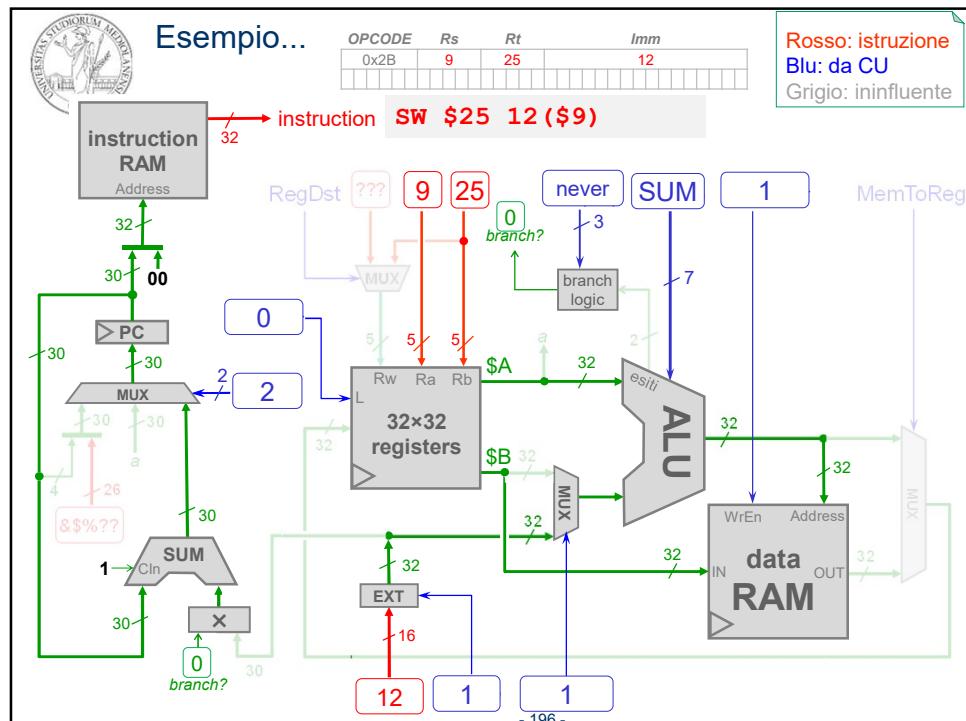

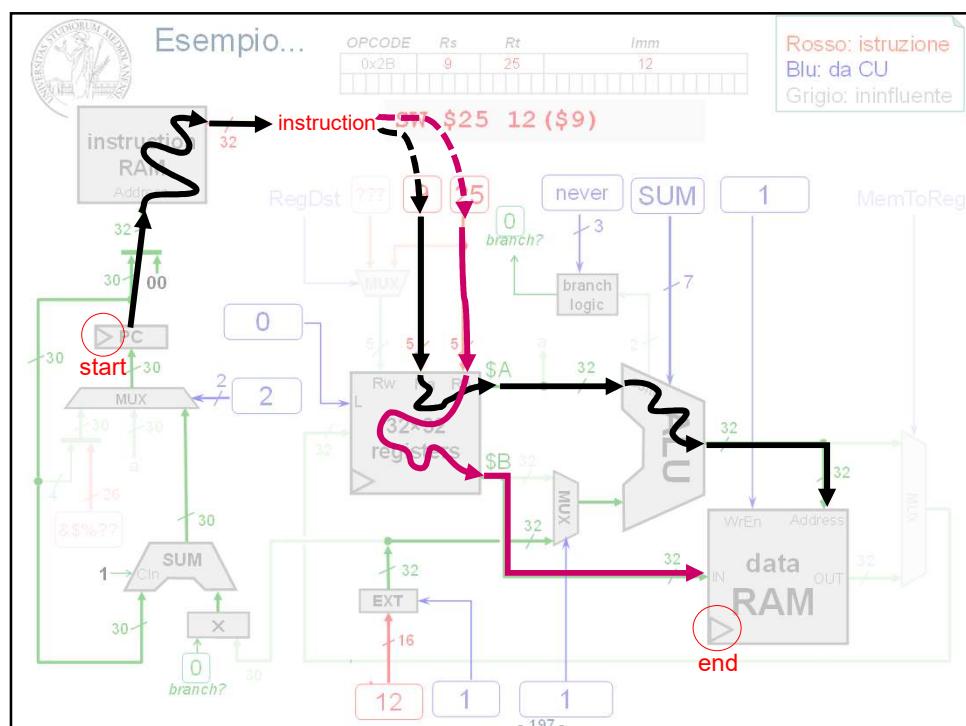

- Analizziamo il datapath per altre istruzioni supportate dal MIPS

- ▶ Vogliamo determinare quale istruzione richiede il tempo di clock più lungo, e quindi la frequenza di clock minima per questa CPU

- 193 -

193

194

195

196

197

198

199

**Un problema con il nostro design:

Cicli Per Istruzione = 1**

Arithmetic & Logical operations

|    |             |          |     |     |     |       |

|----|-------------|----------|-----|-----|-----|-------|

| PC | Inst Memory | Reg File | mux | ALU | mux | setup |

|----|-------------|----------|-----|-----|-----|-------|

Load

|    |             |          |     |     |          |     |       |

|----|-------------|----------|-----|-----|----------|-----|-------|

| PC | Inst Memory | Reg File | mux | ALU | Data Mem | mux | setup |

|----|-------------|----------|-----|-----|----------|-----|-------|

*Critical Path*

Store

|    |             |          |     |     |          |

|----|-------------|----------|-----|-----|----------|

| PC | Inst Memory | Reg File | mux | ALU | Data Mem |

|----|-------------|----------|-----|-----|----------|

Branch

|    |             |          |     |     |

|----|-------------|----------|-----|-----|

| PC | Inst Memory | Reg File | cmp | mux |

|----|-------------|----------|-----|-----|

- CPI = Cycles per Instruction: quanti cicli di clock per ogni istruzione

- Fin'ora, abbiamo ipotizzato CPI = 1

- ▶ Cioè ogni ciclo di clock, si esegue tutta una istruzione

- Svantaggio: il ciclo di clock deve durare abbastanza da permettere l'intera esecuzione dell'istruzione più lenta

Porte logiche

- 200 -

200

**Limiti delle architetture CPU

con CPI = 1**

- È uno spreco che operazioni potenzialmente brevi debbano durare tanto quanto quelle lunghe.

- ▶ In particolare, l'accesso alla RAM può essere molto più lento del resto

- Peggio ancora: gli accessi alla RAM richiedono un tempo variabile (nonostante si chiami così): possono essere davvero lenti (anche centinaia di volte il tempo di commutazione della CPU!) ma solo a volte

- ▶ Solo quelli... "sfortunati", cioè quando il dato letto non è disponibile in un livello di cache («cache miss»), che richiede l'accesso a banchi di memoria fuori dal chip della CPU – vedi lezione sulla gerarchia della RAM

- ▶ Statisticamente, la percentuale di cache miss non è grande; la maggior parte degli accessi in RAM tende ad essere un «cache hit»

- E' uno spreco che il periodo di clock debba essere molto lungo in previsione di questo caso pessimo, ma raro! (una load "sfortunata")

- Datapath **a singolo ciclo** (cioè «CPI=1»)

=> **durata del clock lunga**

- Vedremo nella prossima lezione (seppur solo in teoria) come evitare questo

- 201 -

201