Università degli Studi di Milano Corso di Laurea in Informatica, A.A. 2018-2019

#### Eccezioni

#### Turno A Nicola Basilico

Dipartimento di Informatica Via Comelico 39/41 - 20135 Milano (MI) Ufficio S242 <u>nicola.basilico@unimi.it</u> +39 02.503.16294

#### Turno B Marco Tarini

Dipartimento di Informatica Via Celoria 18 - 20133 Milano (MI) Ufficio 4010 <u>marco.tarini@unimi.it</u> +39 02.503.16217

1

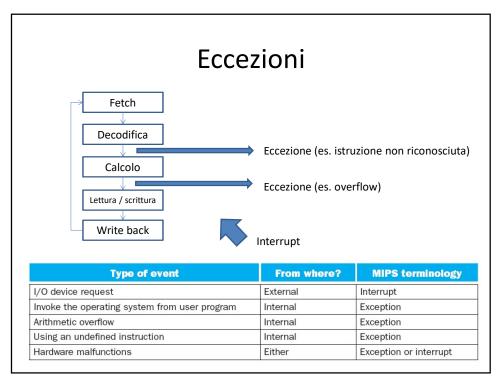

#### Eccezioni

# Atteso: branch e jump cambiamento di flusso Non atteso: eccezioni

- Eccezioni sincrone: dato segmento dati e segmento testo, si verificano sempre ad un tempo *t* determinato (overflow, salti a istruzioni non definite ...)

- Eccezioni asincrone (interrupt): avvengono ad un tempo t non determinato dal programma in esecuzione (I/O, errori hardware, ...)

#### Eccezioni

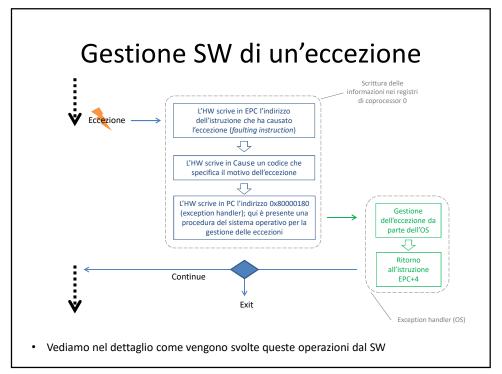

- Le eccezioni vanno gestite attraverso la chiamata ad una procedura speciale: l'exception handler

- Chiamata all'exception handler:

- non prevede né passaggio di parametri, né valori di ritorno

- deve preservare interamente lo stato del programma che ha causato l'eccezione (compresi i registri \$t)

- fa uso di informazioni per la gestione dell'eccezione che l'hardware ha lasciato in alcuni registri speciali

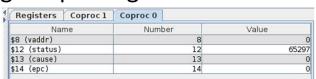

#### I registri per la gestione di eccezioni

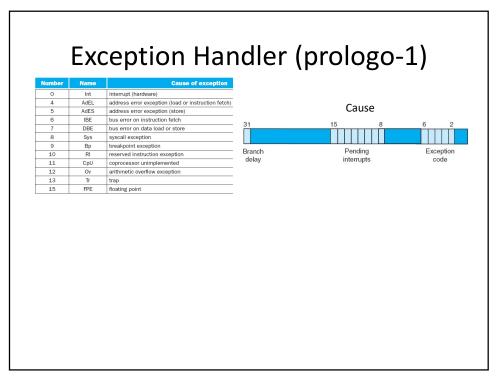

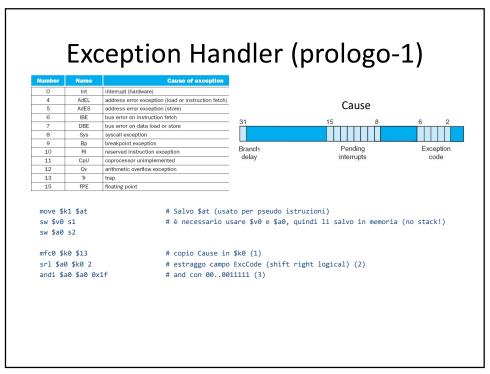

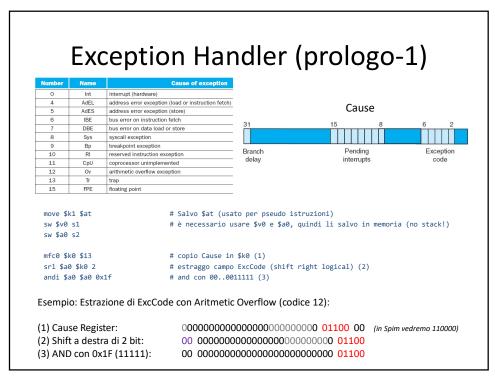

Registro Cause: causa dell'eccezione specificata con **Exception Code** (unsigned int, bit 2-6). Indica anche gli intterupt che al momento dell'eccezione erano ancora da servire

- Registro EPC: exception program counter, indirizzo della word in cui sta la faulting instruction

- Registro BadVaddr: indirizzo errato nel caso di una address exception

- Registro Status: interrupt mask e bit di controllo

5

#### I registri per la gestione di eccezioni

• Registro Cause: causa dell'eccezione specificata da un **Exception Code** (unsigned int, bit 2-6), indica anche gli interrupt che erano ancora da servire

- Registro EPC: exception program counter, indirizzo (nel segmento testo) a cui sta la faulting instruction

- Registro BadVaddr: indirizzo errato nel caso di una address exception

- Registro Status: interrupt mask e bit di controllo

#### Gestione SW di un'eccezione

• Come avviene la lettura e scrittura nei registri del coprocessore 0?

```

# copia dal registro $13 del coprocessore 0 (Cause register) al registro $t0

mfc0 $t0 , $13

# copia dal registro $t0 al registro $14 del coprocessore 0 (EPC)

mtc0 $t0 , $14  # NOTA BENE L'ORDINE DEI PARAMETRI!

# load word dall'indirizzo 100($t3) al registro $13 del coprocessore 0

lwc0 $13, 100($t3)

# store word dal registro $13 del coprocessore 0 in memoria

swc0 $13, 50($t2)

```

10

#### Gestione SW di un'eccezione

- L'exception handler non deve alterare lo stato corrente di registri e memoria

- ha a disposizione due registri riservati \$k0 e \$k1

- nel caso debba fare register spilling, non userà lo stack ma la apposita area .kdata

| ľ     | Nome      | Numero | Utilizzo                           | Preservato durante<br>le chiamate |

|-------|-----------|--------|------------------------------------|-----------------------------------|

| 1     | \$zero    | 0      | costante zero                      | Riservato MIPS                    |

| 1     | \$at      | 1      | riservato per l'assemblatore       | Riservato Compiler                |

| - 3   | \$v0-\$v1 | 2-3    | valori di ritorno di una procedura | No                                |

| 5     | \$a0-\$a3 | 4-7    | argomenti di una procedura         | No                                |

| 1     | \$t0-\$t7 | 8-15   | registri temporanei (non salvati)  | No                                |

| 1     | \$s0-\$s7 | 16-23  | registri salvati                   | Si                                |

|       | \$t8_\$t9 | 24-25  | registri temporanei (non salvati)  | No                                |

| 9     | \$k0-\$k1 | 26-27  | gestione delle eccezioni           | Riservato OS                      |

|       | \$gp      | 28     | puntatore alla global area (dati)  | Si                                |

| 5     | \$sp      | 29     | stack pointer                      | Si                                |

| -   9 | \$s8      | 30     | registro salvato (fp)              | Si                                |

| 3     | \$ra      | 31     | indirizzo di ritorno               | No                                |

#### Gestione SW di un'eccezione

- Suddividiamo logicamente la gestione di un'eccezione nelle tre fasi operative di *prologo, corpo della procedura* ed *epilogo*

- Prologo: stampa le informazioni relative all'eccezione sollevata

- Corpo: valuta la possibilità di ripristinare il flusso di esecuzione e, nel caso di un interrupt, esegue una procedura specifica per la sua gestione

- Epilogo: ripristina lo stato del processore e dei registri, fa riprendere l'esecuzione dall'istruzione successiva a quella che ha causato l'eccezione

12

### **Exception Handler (preambolo)**

Definizione del segmento dati: vengono preallocate le stringhe contenenti i vari messaggi di errore (che dipendono dal tipo di eccezione) e due variabili locali (s1 e s2)

```

.kdata

__m1_: .asciiz " Exception "

__m2_: .asciiz " occurred and

ignored\n"

__e0_: .asciiz " [Interrupt] "

[...]

s1: .word 0

s2: .word 0

```

# Exception Handler (prologo-2)

```

# Stampo informazioni sull'eccezione.

li $v0 4

# syscall 4 (print_str)

la $a0 __m1_

syscall

li $v0 1

# syscall 1 (print_int)

srl $a0 $k0 2

# Extract ExcCode Field

andi $a0 $a0 0x1f

syscall

li $v0 4

# syscall 4 (print_str)

# 3C=00111100

andi $a0 $k0 0x3c

lw $a0 __excp($a0)

nop

syscall

```

# Exception Handler (corpo-1)

Prima cosa da fare: controllare se è possibile riprendere l'esecuzione, altrimenti eseguire exit

```

Se la causa non è «bus error on instruction fetch» (codice 6 (0x18), 00...0011000) allora $pc è valido, in caso contrario in $pc c'è un valore errato e sono necessari controlli aggiuntivi bne $k0 0x18 ok_pc # Bad PC exception requires special checks nop

```

18

# Exception Handler (corpo-2)

Se la causa **non** è «bus error on instruction fetch» (codice **6** (0x18), 00...00**110**00) allora \$pc è

Prima cosa da fare: controllare se è possibile riprendere l'esecuzione, altrimenti eseguire exit

```

valido, in caso contrario in $pc c'è un valore errato e sono necessari controlli aggiuntivi

bne $k0 0x18 ok_pc  # Bad PC exception requires special checks

nop

Se è proprio un errore di fetch, controllo se in EPC ho un indirizzo valido (sintatticamente)

mfc0 $a0 $14  # copio EPC in $a0

andi $a0 $a0 0x3  # Is EPC word-aligned? (0x3=11)

beq $a0 0 ok_pc  # branch se gli ultimi due bit di EPC non sono 1 (divisibile per 4)

nop

```

# Exception Handler (corpo-3)

Prima cosa da fare: controllare se è possibile riprendere l'esecuzione, altrimenti eseguire exit

```

Se la causa non è «bus error on instruction fetch» (codice 6 (0x18), 00...0011000) allora $pc è valido, in caso contrario in $pc c'è un valore errato e sono necessari controlli aggiuntivi

bne $k0 0x18 ok_pc  # Bad PC exception requires special checks

nop

Se è proprio un errore di fetch, controllo se in EPC ho un indirizzo valido (sintatticamente)

mfc0 $a0 $14  # copio EPC in $a0

andi $a0 $a0 0x3  # Is EPC word-aligned (0x3=11)?

beq $a0 0 ok_pc  # branch se gli ultimi due bit di EPC non sono 1 (divisibile per 4)

nop

Nel caso in cui anche EPC non sia valido, non mi resta che fare exit (l'esecuzione non può continuare dopo l'eccezione).

1i $v0 10  # Exit on really bad PC

syscall

ok_pc:

...

```

20

# Exception Handler (corpo-4)

Controllo se c'è stato un interrupt. In quel caso verrà gestito con del codice specifico.

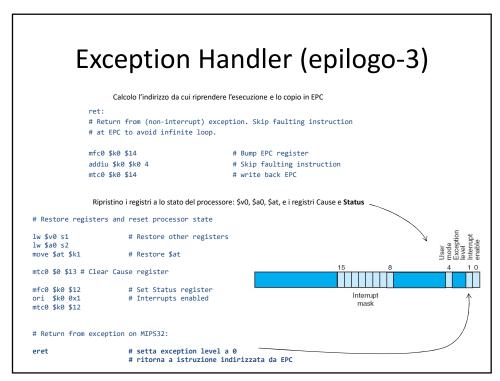

# Exception Handler (epilogo-1)

Calcolo l'indirizzo da cui riprendere l'esecuzione e lo copio in EPC

22

#### Exception Handler (epilogo-2) Calcolo l'indirizzo da cui riprendere l'esecuzione e lo copio in EPC # Return from (non-interrupt) exception. Skip faulting instruction $\mbox{\tt\#}$ at EPC to avoid infinite loop. mfc0 \$k0 \$14 # Bump EPC register addiu \$k0 \$k0 4 # Skip faulting instruction # write back EPC mtc0 \$k0 \$14 Ripristino i registri a lo stato del processore: \$v0, \$a0, \$at, e i registri Cause e **Status** # Restore registers and reset processor state # Restore other registers move \$at \$k1 # Restore \$at mtc0 \$0 \$13 # Clear Cause register mfc0 \$k0 \$12 ori \$k0 0x1 mtc0 \$k0 \$12 # Set Status register # Interrupts enabled Interrupt mask

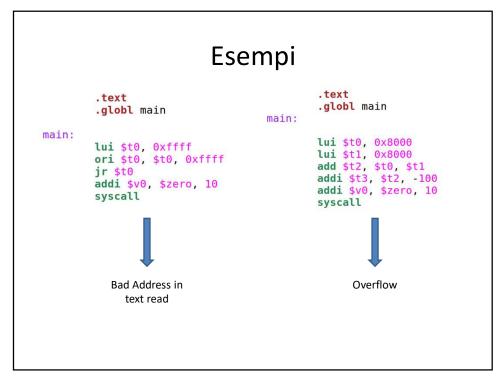

# Esempio • Cosa succede quando facciamo una jump a 0xFFFFFFFF (l'esempio nelle prime slides)? E' un'eccezione di codice 6? bne \$k0 0x18 ok\_pc nop Sì Calcolo indirizzo dell'istruzione da cui ripartire (EPC+4): mfc0 \$k0 \$14 addiu \$k0 \$k0 4 mtc0 \$k0 \$14